先週の続きで、今回もIEDM(International Electron Devices Meeting)でのインテルの発表を解説しよう。ただ先週と異なり、今週は直近のロードマップに絡む話が一切ない。そのずっと先、10年先の話である。

IEDMにおけるインテルの発表論文は以下の9本である。

| IEDMにおけるインテルの発表論文 | ||||||

|---|---|---|---|---|---|---|

| 論文No. | 論文テーマ | |||||

| 27.3 | Enabling Next Generation 3D Heterogeneous Integration Architectures on Intel Process | |||||

| 7.5 | Gate length scaling beyond Si: Mono-layer 2D Channel FETs Robust to Short Channel Effects | |||||

| 28.5 | Characterization and Closed Form Modeling of Edge/Top/Hybrid Metal-2D Semiconductor Contacts | |||||

| 6.7 | Hafnia-Based FeRAM: A Path Toward Ultra-High Density for Next-Generation High-Speed Embedded Memory | |||||

| 13.1 | Multi-domain Phase-field Modeling of Polycrystalline Hafnia-based (Anti-)ferroelectrics Capable of Representing Defects, Wake-up and Fatigue | |||||

| 35.1 | Scaled Submicron Field-Plated Enhancement Mode High-K Gallium Nitride Transistors on 300mm Si(111) Wafer with Power FoM(RONxQGG) of 3 mohm-nC at 40V and fT/fMAX of 130/680GHz | |||||

| 36.4 | Low voltage and high-speed switching of a magnetoelectric element for energy efficient compute | |||||

| 22.5 | A Scalable In-Memory Clustered Annealer for Travelling Salesman Problems with Temporal Noise of FinFET | |||||

| 8.4 | Mitigating Impact of Defects On Performance With Classical Device Engineering of Scaled Si/SiGe qubit arrays | |||||

このうち22.5の、巡回セールスマン問題を解くためのIn-Memory Clustered Annealerは、筆頭筆者はジョージア工科大のAnni Lu博士で、インテルは共著者として3人が名前を連ねているに留まるので、ややインテルの発表とは言い難い。さらに、先頭の27.3は先週解説した内容なので、その他の論文を簡単に紹介したい。

TDMを使ってシリコンよりも高速かつ薄いトランジスタを構築

まず7.5は、TMD(Transition Metal Dichalcogenides:遷移金属ジカルコゲナイド)を使って2Dナノシートを構築、これでGAA(Gate All Around)構成のトランジスタを構築するという論文である。

実際にこれを利用するとGAAの効率をずっと引き上げられる、というのが“Vision”である。

GAAというか積層ナノシートは、縦方向にシートを積むことで駆動電流を増やせるが、左が従来型のシリコンベースのGAAで、右は今回の積層ナノシートを利用した場合の構成になる。

これによりゲート長を5nmあたりまで縮められるとともに、電荷の移動量を増やし、かつ低消費電力にできるというものだ。下の画像は実際にナノシートを挟むかたちでGAAをスタックした試作品の断面構造である。

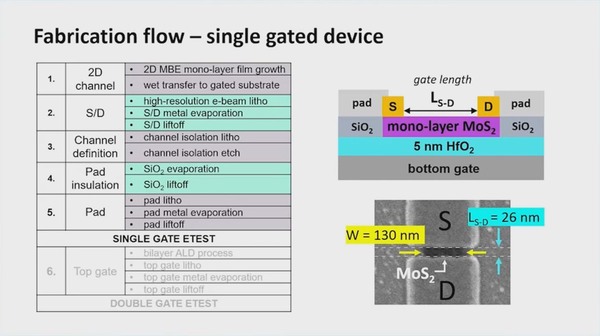

ちなみに下の画像がシングルゲートの場合の作り方である。予想どおりであるが、露光はEUV(極端紫外線)ではなく電子ビームである。

電子ビーム露光はEUVよりはるかに解像度が高いので、微細なパターン描画ができる(電界放出型で0.1nm程度、電子放出型でも1nm未満で描画可能)うえ、高価なマスクを製造する必要もないが、スループットがEUVに輪をかけて低いため、量産にはまるで適さない。

ただ研究用途にはこれで十分であり、逆に言えばこれを量産に持っていくためにはEUVでこの工程を実現するための技術開発が必要になる。今回の発表は、世代的に言えばIntel 18Aの先の先くらいの話であるが、そうした技術開発も怠らない、という内容である。

このナノシートに絡む発表が28.5である。

シートそのものは先の28.5と同じくTMDである。これを金の電極とどうつなぐか、というのが左図。中央はこのコンタクトがどこで利用されるかという話、右は接続部の電流の流れ方をシミュレーションしたものである

ナノシートはどこかで電極につなげる必要がある。このつなげ方でEdge Contact(端だけを接触する)とTop Contact(面で上から抑え込むように接触する)、それとHybrid Contact(L字型をした電極に差し込む形で、面と端の両方で接続する)の3種類の接続方法について比較した、という話である。

上の画像が、断面のシミュレーション画像で、結果から言えば金の端子に溝を掘り、そこにTMDのナノシートを差し込むような形になる。ここで色が寸法当たりの電流量になる。金の端子とTMDの所が色が濃いことで、ここで電流が大量に流れているのがわかるかと思う。

そもそもGAAで複数のトランジスタを積層する理由は駆動電流を増すためであり、したがってナノシートに大量の電流を流せるようにするためには、端子とシートの間の接続にも工夫が要るというわけだ。

もっともこの論文では、Hybrid Contactにすると電流量は増えるが、同時に抵抗も増えることが示されており、この部分をさらに改善するための研究が今後必要とまとめられているあたり、これもまだ先の先の技術ではある。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ