40bitもの巨大な仮想アドレスを保有

ただしなぜ40bitにしたのか謎

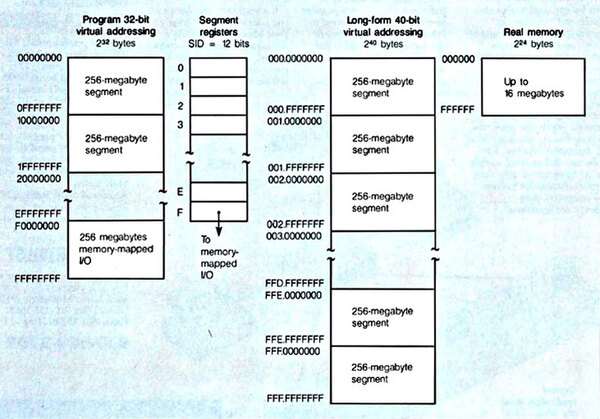

ROMPの仮想記憶は、物理的なメモリーは最大16MBまで対応ながら、仮想アドレスは40bitという結構巨大なサイズである。ただしこれ、12bit(0~4095)のセグメントに分かれた28bit(256MB)のメモリーエリア、というややおもしろい構成である。

画像の出典は、Internet Archives保有のBYTE Magazine Volume 11, Number 11の“Inside the IBM PCs”という特集号

ページサイズは2KBで、12bitのセグメントIDと17bitのページナンバー、11bitのページ内オフセットという形になる。まだこの当時、この40bitをフルに利用できるOSは存在していないが、それに向けて32bitの仮想記憶マシンとして使うことももちろん可能だった。

ただ逆に言えば、なぜ40bitの構成にしたのかの説明がついぞ見つからなかった。強いて 言えば、IBM System Journalの中に“ROMP is a good architectural base for future growth”(ROMPは将来の発展のベースとなる良いアーキテクチャーである)という文言があるあたり、この当時はROMPをベースに製品を展開していくつもりだったのかもしれないが、発展する前にROMPそのものの寿命が尽きたあたりが皮肉ではある。

最終的にROMPは1981年、2チップ構成で完成した。プロセッサー本体は4万5000トランジスタでダイサイズは58.52mm2、MMUが6万1500トランジスタでダイサイズは81.36mm2である。

先に書いた通り、どちらもIBMの2μm NMOSプロセスで製造されている。ソフトウェアとしては、こちらもまずPL.8が移植され、次いでこれを利用してさまざまな言語が移植されることになった。先ほどの4.3MIPSやIBM 801の15.1MIPSという数字は、いずれもPL.8を利用した場合の数字である。

画像の出典は、Wikipedia

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ