今回はASCIシリーズの第1弾であるASCI Redを解説する。前回、CTBT(包括的核実験禁止条約)の話を1995年11月から始めたが、実際には1992年あたりからその動きは始まっていた。

ASCI Red

具体的にはブッシュ(父)政権の際に、1994年度以降は核実験を行なわないことを政治決断したあたりから、CTBTの動きが明確になっていた。このため、完全な核実験は1992年9月23日にネバダ州で行なわれたのが最後である。それゆえに、1995年にCTBT批准を明らかにする前から、DoE(米エネルギー省)では規定路線となっていた。

こうした状況を背景に、1995年1月にニューメキシコ州のサンタフェにあるBishop's LodgeというホテルでDoEの関係するメンバーに加え、ローレンス・リバモア、ロスアラモス、サンディアの3つの国立研究所のメンバーも集めて、ASCIの初期戦略ミーティングが開催される。

ずいぶんこのミーティングは紛糾したらしいのだが、最終的にDoEでASCIのアーキテクトのポジションについていたGil Weigand博士が、ASCIの最初のプラットフォームであるASCI Redは超並列コンピューターで行くことと、そのシステムがアルバカーキ(ニューメキシコ州)にあるサンディア国立研究所の施設に設置することを宣言した。

もともとサンディア国立研究所はインテルのParagonを導入(関連記事)しており、超並列コンピューターにはある程度慣れているということも関係していた。当時ローレンス・リバモア国立研究所とロスアラモス国立研究所はまだCRAYベースのベクトルマシンを利用していたからである。

一度方針が決まると後は早い。この時点でのASCI Redのターゲットは1TFLOPSであった。すでにインテルのParagonはサンディア国立研究所に設置していたマシンで143GFLOPSを、富士通が航空宇宙技術研究所に納入したNWT(Numerical Wind Tunnel:数値風洞)が170GFLOPSをそれぞれ記録していたものの、1TFLPOSにはまだだいぶ遠かった。

ASCI Redでは一足飛びにこれを実現しよう、というある意味意欲的な計画だったが、そのくらい背伸びをしないとASCIの“Accelerated”にはならない、ということだったのかもしれない。

iPSCやTouchstoneを手がけた部隊が

ASCI Redの開発に携わる

1996年度の予算のうち1500万ドルがASCI Redのために確保されるとともに、1995年4月にはASCI Redの提案依頼書のドラフトも公開された。同年5月にはメーカーからの提案の評価が始まり、6月8日と9日にメーカーを交えての審議も行なわれた後で、インテルがASCI Redの契約者として選ばれることになった。最終的にDoEはインテルと9月7日に契約を交わしている。

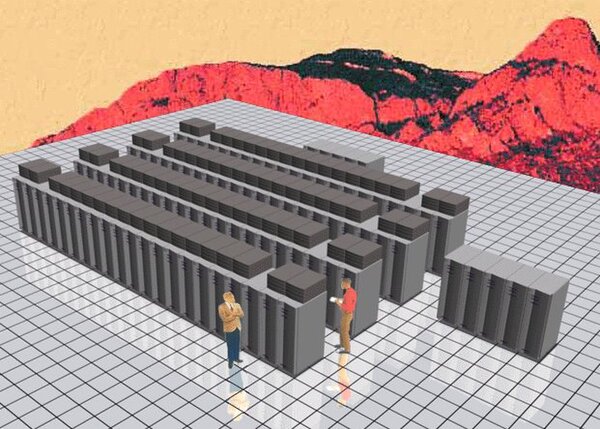

ASCI Redは9216プロセッサーと640基のHDD、1540の電源ユニット、それに616のインターコネクション装置から構成されることになる。左下の画像はASCI Redのイメージ図で、右下の画像が実際の装置写真である。おおよその設置面積は1600平方フィートで、当時の資料によれば「バスケットコートの3分の1」とされた。

この契約を受けてインテルで作業を担当したのは、Justin Rattner率いるSSL(Scalable Server Laboratory)である。

SSLはその後SSD(Scalable System Division)と名前を変えたという話は連載282回で説明したが、要するにiPSCやTouchstoneを手がけていた部隊がそのままこれに携わることになった。

ここからのインテルの作業は早かった。契約から約1年後になる1996年10月7日、部分的に納入したシステム(11キャビネット分)だけを稼動し、208GFLOPSを記録する。

その後も納入分の追加にあわせて性能を高めていき、1996年11月22日には327GFLOPSを達成する。1996年12月4日にはシステム納入前のインテルの施設でのテストで1TFLOPSを超えたことが確認された。

翌1997年6月のTOP500では、7264コア(おおよそ35キャビネット分)を使い、1068.0GFLOPSのスコアを出して、堂々トップとなる(関連リンク)。ちなみにこの1997年6月のリストで2位に入ったのは筑波大学計算科学研究センターのCP-PACS/2048であるが、性能は368.2GFLOPSでASCI Redの3分の1程度でしかない。

ただ、そのCP-PACS/2048も1996年11月には1位だったわけで、いかにASCI Redが大幅に性能を改善したのかが、わかろうというものだ。ちなみにそのTOP500リストが出た直後の1997年6月12日には、全キャビネットの納入が完了、フルシステムで1.338TFLOPSという性能を叩き出して、運用開始となっている。

(→次ページヘ続く 「ASCI Redの内部構造」)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ