Gate arrayより細かいCell Base

アナログ部品を加えたAnalog Master Slice

もう一段細かいのがCell Baseである。こちらはGateよりさらに細かい、個々の部品単位のCellと呼ばれるものをあらかじめレゴブロックのように用意しておき、これを基板(Base)上に配置して相互を配線するというものである。

Cell Baseの仕組み

ちなみにGate ArrayもCell Baseもデジタル回路向けのものだが、これにアナログ部品まで加えたのがAnalog Master Sliceというものになる。こうした出来合いの部品を一切使わずに、完全にイチから開発するのがフルカスタムということになる。

このGate ArrayにしてもCell Baseにしても、基本的な発想は物理設計の容易化である。「あるファウンダリーの特定のプロセスに最適化する」と口で言うのは簡単だが、実際にはパラメーターが非常に多いため、これを実現するのは容易ではない。

そこである程度ファウンダリーの側で最適化したGateもしくはCellを部品の形で用意しておくことで物理設計の手間を省くと共に、最適化には遠いにしても大きく性能が落ちないようにフォローしようというわけだ。

ただしGate ArrayではGateそのものが割と冗長で、配線も無駄が多い。例えば斜め方向の配線はないため、場合によってはあるGate同士を直接接続できず、間に単に信号を伝えるだけのGateを挟むケースもある。Cell Baseはもう少し冗長度が減り効率が上がるが、その分配置配線に時間を要する。

SoCはGate Arrayか

Cell Baseで製造される

ここまでは長い前置き。実を言うと、ほとんどのSoCはこのGate Array、もしくはCell Baseを使って製造されるのが一般的だ。これを俗に「ASIC Gateで製造した」「Standard Cellを使った」などと称する。

理由は単純な話で、一部の大手メーカーを除くと論理設計はSoft IPなどを入手して短時間に済ませており、あとはどうやって物理設計の時間を減らすかがキーになってくる。また、ファウンダリーの提供するプロセスの特徴を熟知していれば別だが、そうでない場合はトラブルをなるべく減らす意味でも、ファウンダリーの提供するASIC Gate/Standard Cellを使う方が安全である。

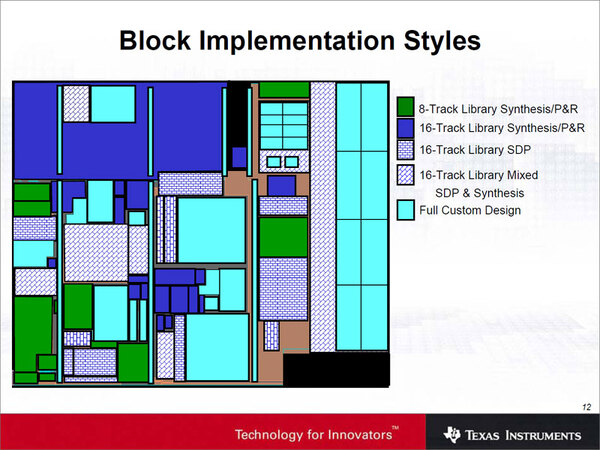

その一方、こうしたASIC GateやStandard Cellを利用すると、どうしても最適化は難しい。前回、TIのF1コアの事例を説明したが、こちらの写真で言うとASIC Gateは“Synthesis/P&R”の部分と、一部SDPの部分に相当する。

ここで“8-Track Library”、“16-Track Library”とあるのが、まさにASIC Gateの種類である。最近、ARMでStandard Cellでの提供を行なっているケースが増えてきているのは、ARMが積極的にファウンダリーと協力関係を築くようになってきたからという話があるが、こうしたものが利用できない場合はASIC Gateを使うか、それともフルカスタムかという選択肢になる。

自由度が高いフルカスタム

それだけにリスクも高い

ではフルカスタムを選ぶとどうなるかだが、これは悪い方向に作用した例を紹介したほうが早いだろう。代表的なものが連載146回で語った「GeForce GTX 480」である。

GeForce GTX 480はVIAの欠陥問題の関係で大変なことになったが、もしもGeForce GTX 480をTSMCのASIC Gateで構成していたら、この問題は出なかっただろうし、Standard Cellでもおそらく問題は大分楽だっただろう。

というのは、ASIC GateやStandard Cellを使う場合、当然ながらファウンダリーが「確実に動作する」構成にするために、VIAの冗長構成は黙っていても入った、というか抜けなかったからだ。この冗長構成をあえて抜くことが可能だったのは、GeForce GTX 480のかなりの部分がフルカスタムで構成されていたためである。ただこの時は、それが悪い方向に作用したわけだ。

ではどうやったらこれを避けられるのだろうか。もう設計者がそのプロセス(この時で言えばTSMCの40nm G)の特徴や癖を理解するしかない。

AMDはRadeon HD 5800世代で40nm Gプロセスを全面的に採用しながらまったく問題はなかった。それはRadeon HD 4750/4730で同じ問題に直面しており、ここでの教訓をうまく生かせたからだ。

要するに、どこのタイミングでつまずいたかの違いでしかない。NVIDIAやAMDは資金力があるから、あるプロセスでの物理実装に失敗しても次の機会にそれを挽回可能だ。しかしこうした資金力を持たないSoCベンダーには、フルカスタムは「当たると大きい(かもしれない)が、外れると会社が傾く」ハイリスク・ハイリターンな選択なのである。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ