Sapphire Rapidsの構成が判明

タイルの面積は約400平方mm

詳細な構成(コア数やSKU)は製品出荷のタイミングで公開する、という話で一切説明はなく、性能という意味ではAMXの性能や、Microserviceでの性能がCascade Lake比で69%向上すると説明しているが、Ice Lake-SP比だと37%程の向上でしかない辺りは少し「?」ではある。

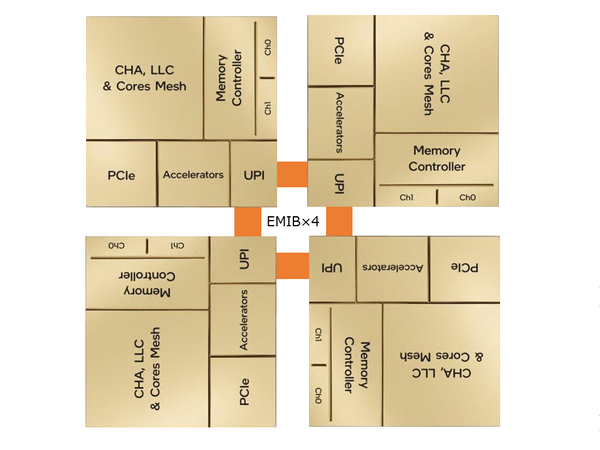

Hot Chipsのカンファレンスセッションでの情報はこの程度であり、メモリーコントローラー周りやPCIe/HBMに関する話は連載629回のスライドで示したものそのままなのだが、カンファレンスに先立って行なわれたチュートリアルセッションでびっくりの情報が出てきた。これはインテルのパッケージ技術の紹介で、実際の製品の構成を説明するものだが、EMIBの実装例としてSapphire Rapidsの構成が出てきた。

ここから以下のことが読み取れる。

- (1)HBMの有り無しでパッケージが異なる

- (2)HBM無しの場合であっても、4つのタイルの接続に10個のEMIBが使われている

それともう1つ、カンファレンスセッションの質疑応答で以下のことも確認された。

- (3)HBMコントローラーとDDR5のコントローラーは別になっている

まず問題になるのが(2)だ。前述のSapphire Rapidsの構成画像を見る限りEMIBは4つであるので、下図のような配置で接続されると想定していた。

この場合、内部は下の図になるという想定だ。各々のタイルから3本づつUPIが出て、うち2本はタイル間の接続に、残る4本が外部接続に利用される格好だ。

これはこれで筋が通ってはいるのだが、EMIB×10だとすると辻褄がまるで合わなくなる。となると、やはり実際には下図のように斜め方向のUPI接続も行なわれている可能性が高い。

構造で言えば下図のような形だ。

問題は、EMIBでどうやってこの斜めの交差を実現するか? である。これに関してまだ明確な説明はなされていないのだが、筆者が考えた案の1つは下図のような立体交差だ。

Tikle 1とTile 4は通常の埋め込み型EMIBを取り、Tile 2と3の間は中にEMIBを仕込んだ立体構造のブリッジを構築、これでつなぐという仕組みである。これが合っているかどうかは定かではないが、10個というEMIBの数を考えるとなにかしらトリックがあると思われる。このあたりは製品発表時に情報が公開されるのではないかと思う(というか、期待したい)。

この連載の記事

-

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 -

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ - この連載の一覧へ