記憶密度が上がると

速度と寿命が低下する

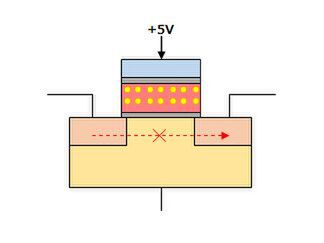

では記憶の読み込みはどうかというと、コントロール・ゲートに5V程度の電圧をかけてやればいい。もしフローティング・ゲートに電子が蓄えられている状態だと、ここでソース→ドレインの間に電流は流れない(図5)。

図5 読み込み時はコントロール・ゲートにわずかな電圧をかける。フローティング・ゲートに電子が蓄えられていると、ソース→ドレインの間に電流は流れないため、値は0になる

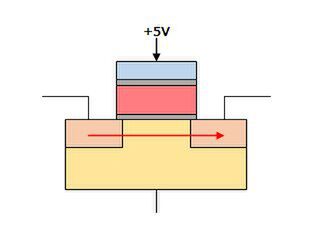

ところがフローティング・ゲートに電子がない状態だと、ソース→ドレインの間で電流が流れることになる(図6)。これにより、値が0か1かを読み出すことが可能になったというわけだ。

図6 フローティング・ゲートに電子がないと、ソース→ドレインの間に電流が流れるため、値は1になる

この構造がSLC(Single Level Cell)と呼ばれる方法だが、より記憶容量を引き上げるため、多値化を図ることになった。

具体的には、電子をフローティング・ゲートに入れる際に、0か1の2段階ではなく0~3の4段階にすることで、2ビット分のデータを保持できるようにするMLC(Multi Level Cell)、さらに0~7の8段階にすることで3ビット分のデータを保持できるようにしたTLC(Tri Level Cell)という技術が導入される。

これによって記憶密度は飛躍的に引きあがるようになったのだが、反面速度と寿命が急速に劣化することになった。もともとフラッシュメモリーの場合、SLCであっても寿命がある。これは、本来トンネル酸化膜に電圧をかけて電子を注入したり引き抜いたりしているわけだが、これを繰り返すとトンネル酸化膜に格子欠陥と呼ばれる絶縁不良の箇所が発生し始める。

この欠陥がトンネル酸化膜を貫通してしまうと、フローティング・ゲートの中の電荷が駄々漏れ状態になり、これ以上記憶状態を保持できなくなる。SLCの場合、この書き込み寿命は数万回~数十万回とされる。

MLC/TLCではなにが問題かというと、いきなり目的の量の電荷をきちんとロードするのは難しいので、例えばMLCで3という値を保持させるなら、まず2を保持させ、そこに1を足す形になる。つまり書き込みの回数が2倍になる。TLCなら4/2/1という3回に分けて書き込み(電荷の継ぎ足し)を行なうことになる。これには次の問題がある。

- 書き込みの時間が原理的に2倍(MLC)あるいは3倍(TLC)かかる。実際には、もうすこし遅くなる。

- 書き込み寿命の減少。MLC/TLCの場合、短期間に複数回の書き込むので、トンネル酸化膜の劣化が加速化する。回数だけで比較すれば、MLCはSLCの2倍、TCLは3倍の書き込み頻度になるので、その分書き込み寿命が2分の1/3分の1になる計算だが、実際にはMLCはSLCに比べて1桁、TCLは2桁書き込み寿命が減少する。

特にこの寿命の問題はMLC/TLCの構造的なものに起因するため、根本的な解決は難しく、結果としてMLC/TLCを利用するときには代替領域、あるブロックが使えなくなった時に、そのブロックを代替する目的で最初から用意されているブロックを多めに準備するなど、ウェアレベリングを強化して特定の領域への書き込みの集中を避けるといった程度の対策しかない。

フラッシュメモリーは微細化すればするほど

エラーの頻度が増加する

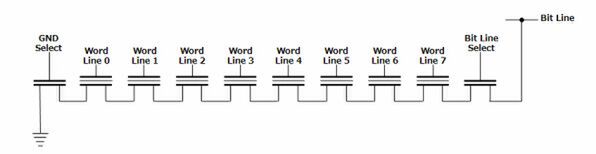

さて、話をもうすこし微細化に進めてゆく。先ほどNANDとNORでは配線が異なるという話をしたが、例えばセルの等価回路を図7のように表記した場合、NANDの回路構造は図8のように示される。

図7 セルの等価回路図

NORフラッシュの場合は、セルの1個ごとにGND/Bit Line向けの配線が用意されるが、NANDフラッシュはある程度まとめた状態で構成される。これによりセル同士を隣接して構築できるので、NORに比べて高密度に実装しやすいという話である。

ではこのまま、さらなる容量増加を求めて微細化するとどうなるか、というのが次の話だ。例えば図8で、Word Line 1に電荷を継ぎ足ししようとすると、隣接するWord Line 0/2のセルにも影響を及ぼしやすい。

それでもSLCでは、値が0か1しかないためまだマシだが、MLC/TLCになると継ぎ足す電荷量が小さいため、隣接するセルの電荷量が変化してしまうことになる。

これは以前から問題になっていたことだが、プロセスを微細化するとセル同士の間隔が物理的に短くなるから、より影響を受けやすくなっている。この結果として、高密度化するNANDフラッシュには強力なエラー訂正が必要になった。

このあたりはSSDの動向を見ているとわかるが、最初はパリティー程度だったのがすぐにECCを搭載するようになり、そのECCのビット数がどんどん増えていった。最近はついにLDPC(Low Density Parity Code:恐ろしく計算に手間がかかる代わりに強力無比なエラー訂正手法)を搭載するとかしないとかの話になりつつあるのは、微細化にともなうエラー頻度の高さを物語っている。

この連載の記事

-

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 - この連載の一覧へ