ロジック回路の遅延が暴走の原因

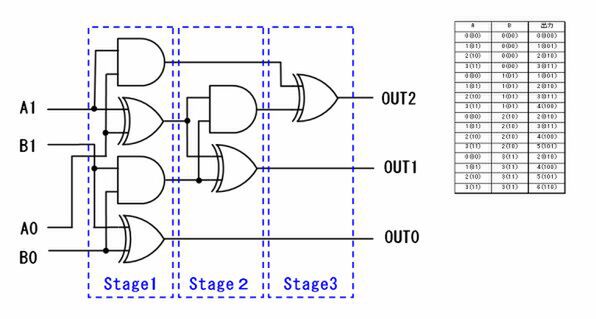

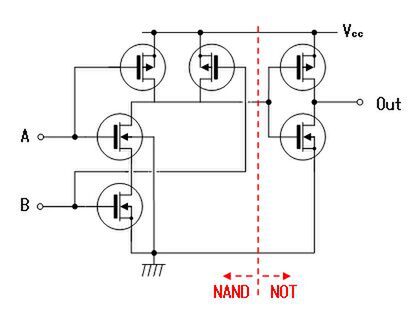

再び話を回路レベルに戻す。図3はXORとANDで構成されているが、これはトランジスタレベルでどう実装されているか、というのが図4である。

図4 AND回路の内部

赤い破線で示した左側がNAND、右側がNOTとなる。ロジック回路ではNAND=AND+NOTであるが、回路的にはNAND回路を直接作る方が楽で、なのでAND=NAND+NOTという構成を取る。

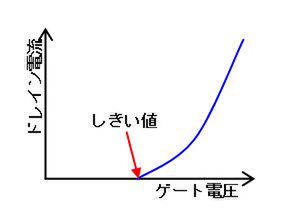

さて、ここで問題になるのはトランジスタのDelayである。図5はNMOS型の動作特性例であるが、ある程度以上のゲート電圧(この境をしきい値電圧と呼ぶ)をかけると電流が流れ始め、ある程度以上の電圧で最大になるというもので、この特性自体は前回説明した通りである。

図5 NMOS型回路の動作特性

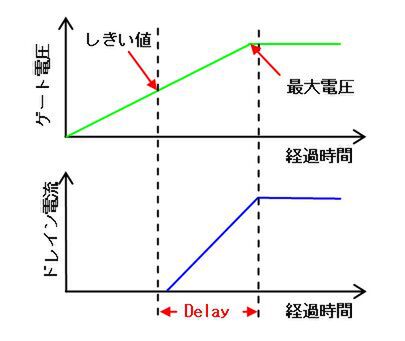

ただ前回説明しなかったのが、経過時間との関係である。図6は横軸に経過時間を取り、縦軸にゲート電圧とドレイン電流の変化を取ったものだ。例えば電圧を閾値~最大に変化させるのには一定の時間がかかる。ドレイン電流も当然これに応じて変化するため、トランジスタの値がデジタル回路的に変わるまでには、一定の時間が必要になる。

図6 NMOS型回路の経過時間による電圧/電流の変化

図6で赤く“Delay”と書いたのがその部分で、これが一般にトランジスタのDelayとして認識されている。このDelayの逆数がトランジスタの速度、あるいはトランジスタのスイッチング速度として認識されている。

ちなみに図6で2つのグラフに若干ずれがあるのは、実際にゲート電圧がしきい値になった瞬間から、ドレイン電流が流れ始めるまでの間にはわずかなタイムラグがあるためだ。これも広義にはトランジスタのDelayに含まれる。

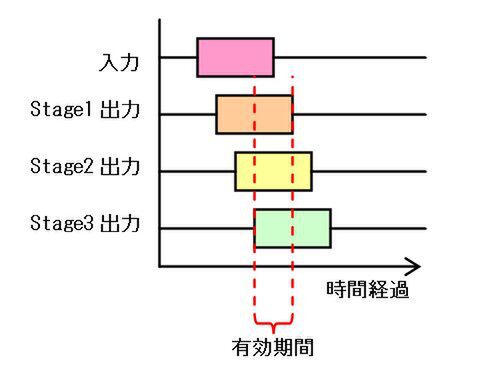

このトランジスタのDelayは、図3のケースでは結構面倒になることがある。図7は図3の2bitの加算器にデータを入れ、結果が出てくる様子を時間軸で見たものだ。

図7 2bitの加算器の動作

まず入力が一定期間続くと、そこから若干(=トランジスタのDelay分)遅れて、Stage 1の出力が出てくる。そこから遅れてStage 2の出力が、さらに遅れてStage 3の出力がそれぞれ出てくる。

2bitの加算器の出力は、Stage 1~3の全部の出力になるため、時間軸で見るとこの3つが全部意味がある出力がある期間は、赤の破線で挟んだわずかな時間でしかない。もちろんこの図は大げさに描いていて、実際はもっとDelayの期間が短いので、もう少し有効期間の幅は大きくなる。それにしても以下の問題は本質的なものである。

- ロジック回路を挟む事で遅延が発生する

- なにもしないと出力の有効期間が限られる

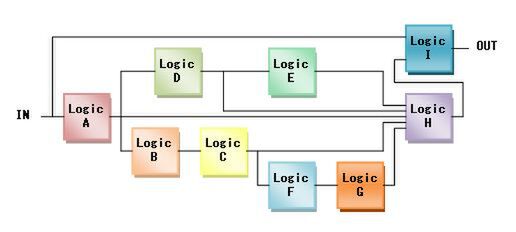

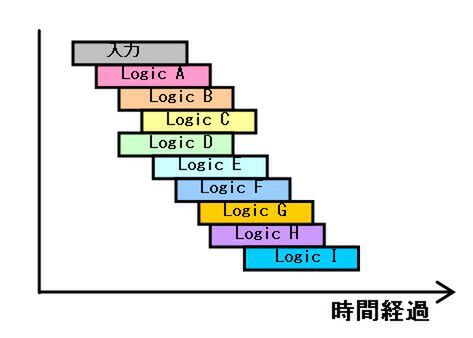

これは特に、回路が複雑になってくるケースで顕著である。例えば図8のような回路があるとする。Logic A~Iはそれぞれ、図3よりももっと大規模なロジック回路から成立していると考えてほしい。

図8 複雑なロジック回路の例

この場合、一番設計が難しいのはLogic Iである。というのは入力の値と、Logic A~Hの各処理を抜けてきた値の両方を使うわけだが、もし各ロジック回路におけるDelayが大きすぎると、図9のようにLogic Iの処理が始まる前に入力が無効になってしまい、正常に処理ができなくなる。

図9 図8のロジック回路が行なう処理

それ以前に、Logic HにしてもLogic A/C/D/E/Gの各入力を使って処理をするわけだが、このLogic Aの入力がタイミング的にギリギリアウトになるから、このままだとそもそも正常に処理が実行できなくなる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ