今回は、9月11日に正式発表となったBay Trailの話題をお届けしよう。

インテル提供のBay Trailパッケージ写真

Bay TrailはSilvermontコアを搭載した、クライアント向けのSoC(System-on-a-chip)製品で、以下の4種類がラインナップされることになっている。

| Bay Trailのラインナップ | |

|---|---|

| Bay Trail-T | タブレット向け |

| Bay Trail-D | デスクトップ向け |

| Bay Trail-M | モバイル向け |

| Bay Trail-I | 組み込む向け |

タブレット向けのBay Trail-T

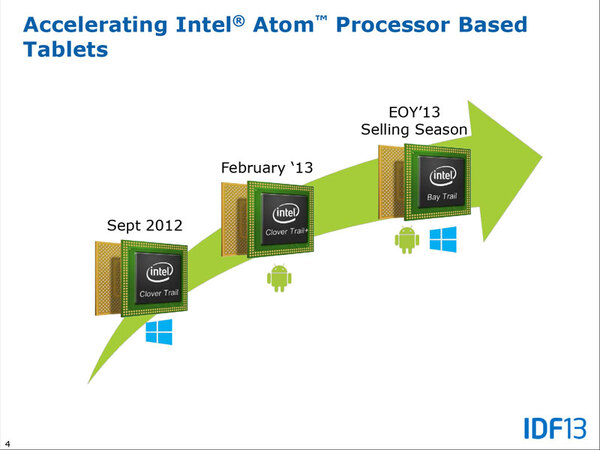

今回はタブレット向けのBay Trail-Tがメインであるため、説明もこちらが主になっている。そのBay Trail-Tは、インテルとしては2世代目のタブレット向けSoCということになる。

これを搭載した製品の発売時期は今年年末(EOY:End Of Year)ということで、IDFでも様々な試作品が展示されていたが、クリスマスシーズンに市場投入されることになるだろう。

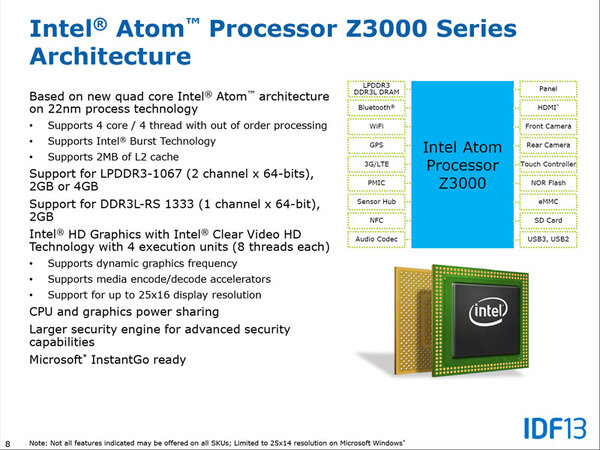

さてそのBay Trail-Tの基本的な構造が下の画像だ。基本的にはSilvermontコアのCPUに、IvyBridgeなどと同じIntel HD Graphics(ただしShader数は8)、それと周辺回路を組み合わせた形である。

メモリーは、携帯電話などに利用されるLPDDR3と、PC向けに利用されるDDR3の省電力タイプであるDDR3L、さらにSelf Refresh時の消費電力を減らしたDDR3L-RSをサポートしている。

おもしろいのは、LPDDR3では2ch(合計帯域は17GB/秒)なのが、DDR3L-RSでは1ch(帯域は10.7GB/秒)に留まっていることだ。これはおそらく2つの理由がある。

1つは消費電力の問題。LPDDR3はそもそも携帯電話などに向けて開発された省電力メモリーなので、動作時の消費電力も低く抑えられている。これに対しDDR3L-RSは、基本的にはPC向けのDDR3を若干低電圧(1.5V→1.35V)にして動作時の消費電力を若干下げた程度である。

“RS”は待機時にリフレッシュする際の消費電力を抑える機構で、稼動時の消費電力には無関係である。結果、タブレット向けのTDPの枠を考えた場合、LPDDR3-1066×2とDDR3L-RS 1333×1がほぼ同じ消費電力であり、ここから制約が生まれたのであろうと想像できる。

もう一つは価格の問題。LPDDR3は、PC向けのDDR3と比較すると非常に高価である。相場で言えば、同じ速度/容量で比較した場合、LPDDR3はDDR3の3~4倍の価格となる。

対してDDR3L-RSは、DDR3とDDR3Lの価格が最近はほぼ同じ程度(強いて言えばDDR3Lが5%前後高価)で、DDR3L-RSはDDR3Lの10%増し程度の価格なので、DDR3比でも15%増しになるかならないかだ。

例えばLPDDR3-1066×2で4GBの構成をとった場合、そのメモリーの価格はDDR3L-RS 1333×1 2GBの5倍以上と推定される。ハイエンド向けのタブレットならばこれは許容されるだろうが、バリュー向けにはかなり厳しい。

インテルとしてはBay Trail-Tでローエンドからハイエンドまでカバーしたいため、メモリーに関しても低コストの構成と高コストながら高性能の構成の両方をラインナップしておきたかったのだろう。

Bay Trail-Tの

ラインナップは6種類

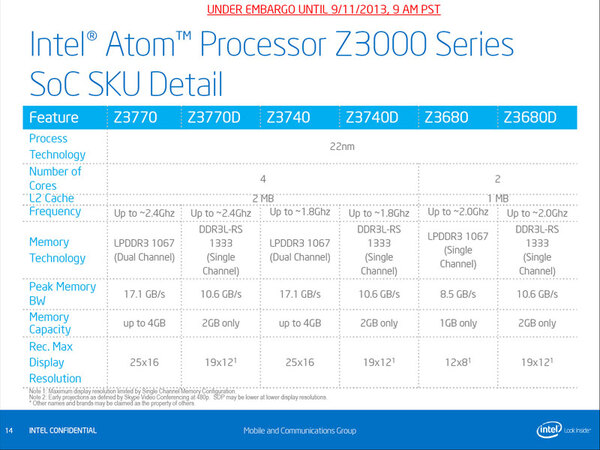

そのラインナップが下の画像だ。4コアの2.4GHz、4コアの1.8GHzと2コアの2GHzという3種類で、それぞれLPDDR3とDDR3L-RSが用意され、合計6製品になる。

ただ2コア品は完全にバリュー向けと割り切られており、LPDDR3の場合でも1chになっている。この結果として、「Z3680」はDDR3L-RSを搭載する「Z3860D」を下回るスペック(最大搭載メモリー量1GB、画面サイズは1280×800ドットが最大)に落ちてしまっている。

このクラスでは、スマートフォンとしてはローエンド向けで、価格以外の差別化要因としては、性能そのものよりむしろバッテリー寿命になりがちなので、やや高価なLPDDR3を使うことにも意味があるとしたのかもしれない。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ