3D V-Cacheを搭載した

Genoa-X

次いでGenoa-Xであるが、こちらはGenoaに3D V-Cacheを搭載したモデルである。3D V-CacheをEPYCに搭載した場合の効果というのは連載642回のMilan-Xの時にも説明した通りだ。

当たり前だがなんでも性能が上がるというわけではなくキャッシュ増量の効果が得られるアプリケーションに限るし、また構成的にも増量したキャッシュがうまく使えるようなケースに限られるが、そうした条件をうまく満たすと大幅に性能が上がることがわかっている。

これは今回のGenoa-Xにもそのまま当てはまる。まずSKUであるが、下の画像の3製品のみである。

96コアのEPYC 9684XのみTDPがやや高いのはわかるが、400Wというのは驚き。スペック的にはEPYC 9654と大きくは変わらない(Baseが2.4GHz→2.55GHzとやや高い)のに、なぜ40W多いのか? EPYC 9684X以外は8ダイ構成である

ちなみにEPYC 9684X、最大ブーストは3.7GHzでEPYC 9654と変わらないが、全コアブーストは3.42GHzとやや刻んできており、EPYC 9654の3.55GHzよりやや低めである。

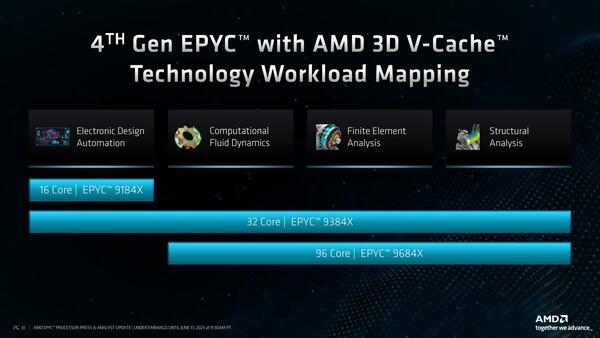

それぞれのラインナップの用途をまとめたのが下の画像で、EDA向けなどにはスレッドあたりの性能が高いことが求められるので16コアのEPYC 9184Xが最適だが、CFDやFEA、構造計算などはトータルの性能が求められるので32コアのEPYC 9384Xや96コアのEPYC 9684Xが向いているという説明である。

ちなみにEPYC 9684Xではコアあたり12MBの3次キャッシュが利用できるわけだが、EPYC 9384Xで24MB、EPYC 9184Xでは48MBの3次キャッシュが利用できることになる。

加えて言えば全製品ともDDR5-4800 12chをサポートしているわけで、スレッドあたりのメモリー帯域やキャッシュ容量が問題になる場合は、必ずしも96コアのEPYC 9684Xではなくより下位モデルの方がトータルでは性能が高いということもあり得るわけで、このあたりはアプリケーション要件に応じて選べばよいという姿勢である。

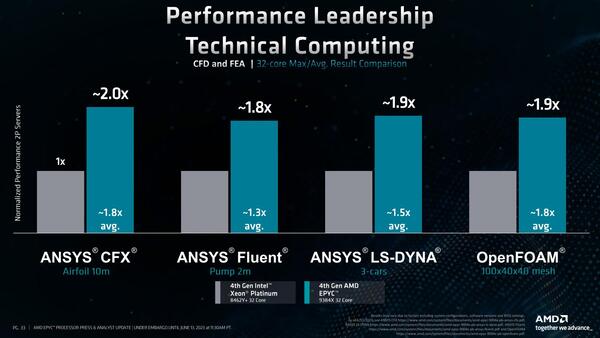

実際に、Sapphire Rapidsとの性能比較が下の画像だが、これも当然条件次第なところがある。

なおマイクロソフトは今回も、Genoa-Xを実装したHBv4 Instanceの性能を開示している。今回は分析はしないが、結果から言えば以前のMilan-Xの時のように、なんでもかんでも性能が上がるわけではないが、うまくスイートスポットにはまれば(Genoaと比較しても)性能が向上することが示されている。

マイクロソフトはこのHBv4 Instance、当初はGenoaベースでプレビューを提供していたが、今後すべてをGenoa-Xに更新の上で正式にサービスを提供する予定である。

この連載の記事

-

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 -

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ - この連載の一覧へ