Xeon E7 v4シリーズが6月6日に発表

BroadwellコアのXeonがすべて出そろう

さて、ここまでは見えている範囲の話であるが、ここからは確度がグンと下がる話になる。最大8P構成が可能なXeon E7 v4シリーズも6月6日に発表され、これでやっとインテルはXeon向けのBroadwellコアの出荷を、Top to Bottomで完了したことになる。

このBroadwellコアはいずれも前のHaswellベースコアとソケット互換であり、Xeon E7/Xeon E5がLGA 2011、Xeon E3がデスクトップと共通のLGA 1151である。

といっても実際にはXeon E7とXeon E5ではプラットフォームそのものが異なっている。パッケージもピン数は同じだが、Xeon E5がSocket R3、Xeon E7はSocket R1で異なっている。

これを統合化するという話が出ており、これはPurley Platformと呼ばれている。このPurley Platformはもちろん正式発表されたものではないのだが、いろいろ漏れ聞こえてくるところをまとめると以下のようなものになるらしい。

- パッケージはLGA 3647ベースのSocket P。Xeonに加えてXeon Phiにも対応

- 2P/4P/8Pで共通

- DDR4×6ch構成。最大DDR4-2666まで対応。ただし2 DIMM/chまで。RDIMM/LRDIMMをサポート

- プロセッサー間インターコネクトとして、従来のQPIに代わりUPIと呼ばれる新しいものを利用する。転送速度は9.6/10.4MT/秒とされるが、バス幅や構成などは不明。プロセッサーあたり最大3つのUPIを接続できる

- Lewisburgと呼ばれるチップセットで対応、CPUとはDMI3で接続

- PCI ExpressはCPUあたり最大48レーン利用可能

ちなみにこのPurleyプラットフォームはSkylake-EP/EXだけでなく、この後に続く予定の10nmプロセスで製造されるCannonlake-EP/EXも同じプラットフォームで引き続きサポートされることになる。登場は2017年後半という話である。

問題は、これはあまりにデスクトップやワークステーション、小規模デスクトップには重厚すぎる構成となることだ。それもあってか、この世代では2つのプラットフォームが新たに追加されることになるらしい。

1つはXeon E3のようなワークステーション/小規模サーバー向けのもので、これはSkylake-Wというコード名になる。パッケージはLGA 2061で、コアは10~18コア程度まで(28コアまでサポートという話もあるが、やや怪しい)とされる。その他の構成は以下のとおり。

- パッケージはLGA-2061のSocket-R(Socket R4?)

- 1P構成のみサポート

- メモリーは4chで、DDR4-2667までサポート

- CPUからPCI Expressを最大48レーン利用可能

- チップセットにはKabyLake PCH(Z270あるいはH270あたり?)をサポート。チップセットとはDMI3で接続

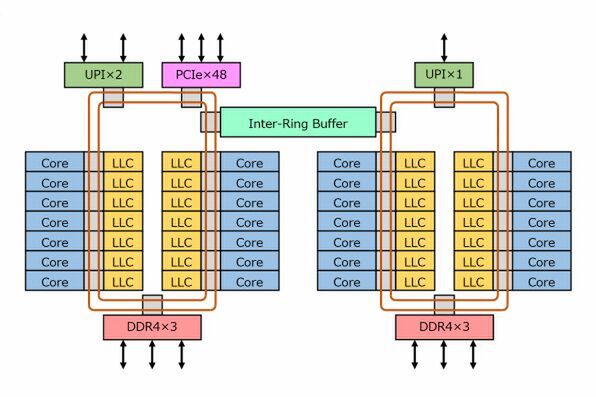

なお、コアそのものはSkylake-EP/EXと同じものであろうと思われる。下図は、仮にSkylake-EP/EXがBroadwell-EXまでの構造を踏襲したと仮定した場合の構造(ただし28Pの場合)である。

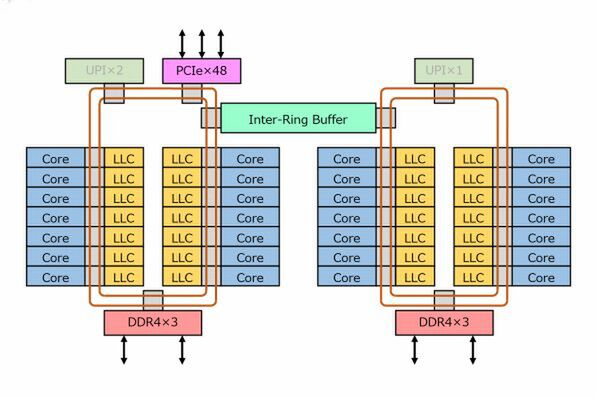

もしこのコアをSkylake-W向けに出す場合、構造は下図のようになるだろう。単にUPIを無効化し、DDR4のメモリーコントローラーを4chだけ有効にするという形だ。UPIとDDR4×2を無効化すれば、必要なピン数は現在のLGA2011-3と大して変わらないから、現実的にはこのような形になるだろう。

ただここではわかりやすく書くために、ハイエンドの2リング構造となるHCC(High Core Count)ダイを例に引き出したが、実際はSkylake-Wは1リング構成のLCC(Low Core Count)ダイと、1.5リング構成のMCC(Middle Core Count)ダイが使われ、HCCダイは使われないように思う。

このSkylake-W向けのプラットフォームにはBasin Fallsという名前が付いている。このBasin Fallsもやはり2017年後半に投入されるようだ。

いよいよ謎なのが現在のBroadwell-Eの後継である。Skylake世代では、ここにSkylake-XとKabyLake-Xという2種類のCPUコアを投入するとしている。ただそのプラットフォームがどうなるのかに関しては情報がなく、現状伝えられているのは以下の事象のみである。

- Skylake-XはTDP140Wで6/8/10コア

- KabyLake-XはTDP95Wで4コア

普通に考えると、KabyLakeのK付き(つまりSkylakeで言えばCore i7-6700Kに相当する製品)がKabylake-Xとしてリブランド。プラットフォームは既存のLGA 1151をそのまま利用するか、Skylake-XはSkylake-Wを転用したBasin Fallsを利用して投入というあたりだろう。

間違ってもハイエンドデスクトップ向けに新しいプラットフォームを投入したりはしないはずなのだが、これに関しては明確な情報がない。

このあたりは、KabyLake-Sの投入の時期にもう少しクリアになるのではないかと思うが、早くて年末。遅いと来年1月になりそうである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ