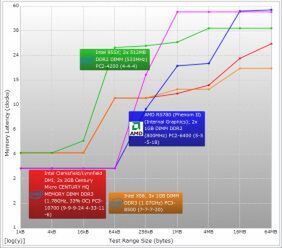

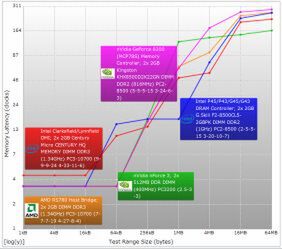

問題は「どの程度待たされるか」である。一例として、手元にあったCore i5-750(2.66GHz)を使って、総合ベンチマークソフト「Sandra 2010」のMemory Latencyテストを実行してみた。

左がシーケンシャルアクセスの場合で、1次キャッシュにヒットする範囲では3~4サイクル、2次キャッシュだと10~20サイクル程度で済むが、メモリーアクセスになると50サイクル以上必要になる。右はランダムアクセスのケースで、こちらではさらに酷くなっているのがわかる。特にメモリーアクセスでは、200サイクル以上要している。

つまり、何も工夫しないでメモリーアクセスが発生してしまうと、図2のようにただ漠然とパイプラインを止めて数百サイクル待機する、というばかげた状況に陥ることがわかる。このケースでは、15命令の処理に124サイクル必要とするわけで、図1の理想的な動作の、20%の性能しか出せないことになる。

メモリーとCPUの速度差を埋めるキャッシュの活用

これを避けるためにはどうするか? まず最初のアイディアが「キャッシュの利用」である。80286あたりの世代までは、CPUとメモリーの速度にそれほど大きな乖離がなかった。ところが80386世代の後半から、次第にCPUの速度がメモリーの速度を大幅に上回るようになる。そのためメモリーアクセスだけで済ませると、メモリー速度の遅さに足を引っ張られるようになってきた。

そこで、CPU側あるいはチップセット側にキャッシュメモリーを用意することで、スピードの差を埋めるという方策がとられるようになった。ただしキャッシュも万能ではなく、またダイサイズを低く抑えるという観点からも、そうそう大量のキャッシュは搭載しにくい。これを補うため、キャッシュに階層構造を設けたり、キャッシュ管理を工夫したり、キャッシュの構成自体を工夫したりとさまざまなテクニックが利用されるようになった。

また、キャッシュをいくら積んでも、そこに必要とされるデータが入っていないと意味がない。これを解決するために、「プリフェッチ」(データの先読み)と呼ばれる技法が広く使われている。より積極的にプリフェッチを実現するために、「ヘルパースレッド」「Victim Thread」などと呼ばれるマルチスレッド技法もある。もっともこちらは引き続き研究が続けられているようだが、これを最初に搭載する予定だったのが幻のインテルCPU「Tejas」とみられているだけに、その後もこれを積極的に利用した例は現れていない。

もっと積極的に、「そもそもデータをキャッシュなりレジスターに取り込むまで、パイプラインに命令を取り込まない」という、逆転の発想を実装したプロセッサーも存在しており(x86ではないが)、これは「ストールフリーパイプライン」などと呼ばれている。また別のアイディアには、「メモリーアクセスが発生してもパイプラインを止めない」という仕組みがある。これは「アウトオブオーダー」として実装されることになったが、これは別の回で説明することにしたい。

この連載の記事

-

第780回

PC

Lunar Lakeに搭載される正体不明のメモリーサイドキャッシュ インテル CPUロードマップ -

第779回

PC

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ -

第778回

PC

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ -

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 -

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 - この連載の一覧へ