CPUの性能発揮を阻害する「パイプラインストール」

前回に続き、今回もCPUのパイプライン処理について解説する。前回の最後では、「パイプライン段数を無闇に増やしても問題」という話をした。理由のひとつは消費電力だが、これはまた別の話になるので、今回はもうひとつの理由である「パイプラインストール」と「パイプラインハザード」の方を取り上げてみたい。

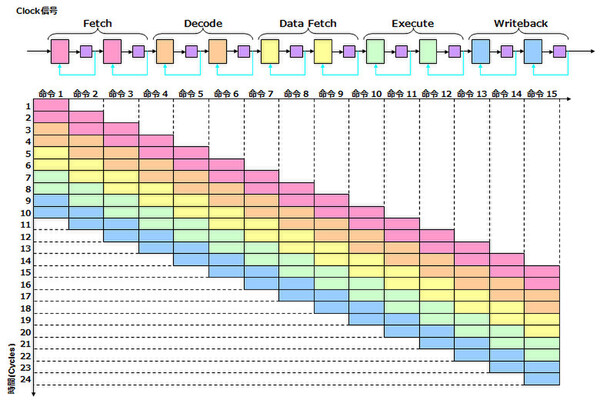

この2つは時々混同されることもあるが、基本的には別の要因で発生する問題であり、対応方法もちょっと異なる。まず前提として図1のようなケースを考えてみる。パイプライン段数は10段となっているため(昨今のx86プロセッサーから言えば短め)、例えば15個の命令を処理するのに要する時間は、合計24サイクルを要する計算だ。

まずパイプラインストールだが、これはパイプラインが「止まる」(Stall)することを示す。よくありがちなのは、Data Fetchだ。これは要するにデータを取り込む処理である。

- C=A+B

例えば、命令3が上の命令「AとBを加算して、Cに結果を入れる」を実行する場合、加算に先立ってAとBの値を確定しなければならない。この値の格納にはCPU内部のレジスターが割り当てられることが多く、この場合は遅れが出ない。通常なら、内部レジスターは1サイクルでアクセスできるためだ。

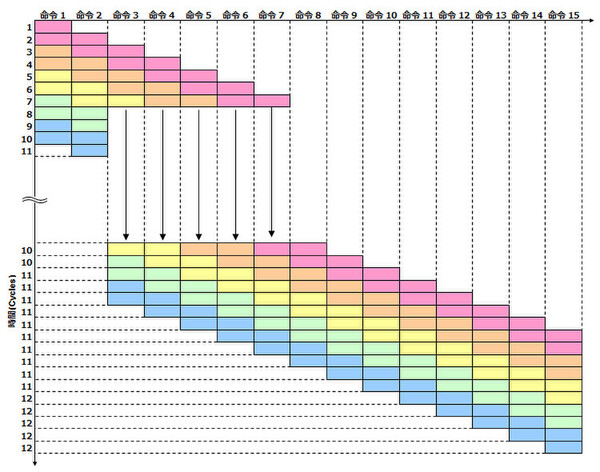

ところがレジスターの数は必ずしも多くないし、レジスターにすべてのデータが入っているとも限らない。どこかでメモリーにアクセスする必要がある。上の命令のケースでは、「Aはレジスターが使えるが、Bはメモリーから値を取得する必要がある」と想定しよう。するとどうなるか? というのが、次の図2である。

7クロック目までは、順調にパイプラインの各ステージが動作する。ところが、7クロック目のData Fetchステージ(図中の黄色部分)でメモリーアクセスが発生すると、パイプラインはそのデータをメモリーから読み込むまで、待機することになる。図1を見直してもらうとわかるが、パイプラインの場合は「あるステージが待機すると、それ以後のステージも全部待機せざるをえない」という欠点がある。そのため命令3以降の処理は全部、メモリーアクセスから帰ってくるまで待機することになる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ