ロードマップでわかる!当世プロセッサー事情 第659回

ISSCC 2022で明らかになったZen 3コアと3D V-Cacheの詳細 AMD CPUロードマップ

2022年03月21日 12時00分更新

同じトランジスタを使いつつ消費電力減を実現

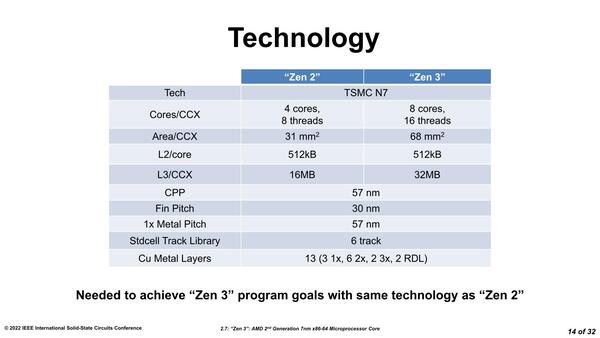

ついでに、トランジスタ周りの話も説明したい。まず基本的なパラメーターだが、Zen 2とZen 3では基本的に同じプロセスなので、プロセス自体をいじって性能を上げることはできない。

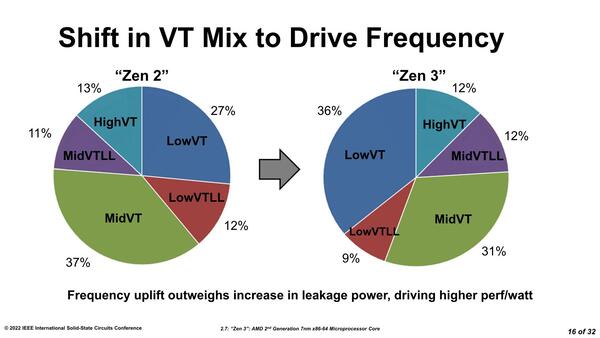

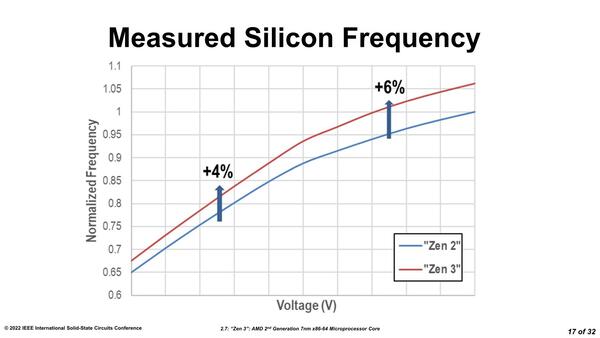

そこで、同じトランジスタを使いつつ、Zen 2→Zen 3ではそれぞれ動作周波数を4~6%引き上げることを目標にしたとする。また、トランジスタもMid VT(中間的な電圧)やLow VT(低電圧)を使う比率を高めており、全体的に消費電力を下げる工夫が効いているとした。

| トランジスタの比率 | ||||||

|---|---|---|---|---|---|---|

| Zen 2 | Zen 3 | |||||

| High VT | 13% | 12% | ||||

| Mid VT | 48% | 43% | ||||

| Low VT | 39% | 45% | ||||

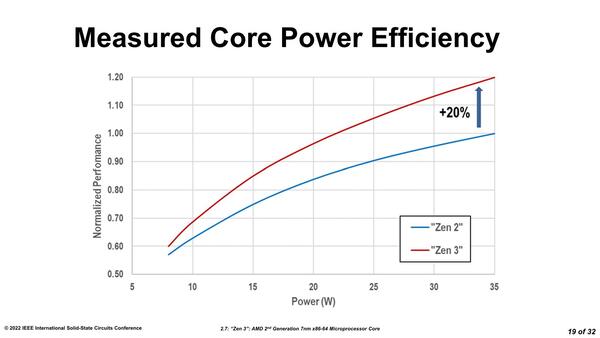

この結果として、同じ消費電力での動作周波数は、4~6%向上したとしている。もちろんIPCを引き上げる工夫もZen 2→Zen 3ではあり、結果としてトータルで20%ほどの性能/消費電力比の向上が実現した、という話である。

ということで、なんとか実際に製品が出る前に、3D V-Cacheにまつわる話ができた。あとは実際に性能はどうか? で、これは製品が入手できてからのお楽しみである。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ