COMPUTEXでは見事に姿を消した8コアのCoffee Lakeであるが、やっと出荷時期などが決まったようで、いろいろ情報が流れてきたので、このあたりでまとめておきたい。ただその前に余談というか直接関連しない話を2つ紹介しよう。

第9世代Coreプロセッサーとなる8コアのCoffee Lake

今年中にCascade Lakeを投入

その後継はCooper Lakeと判明

まず8月8日、インテルは2018 Data-Centric Innovation Summitというイベントを開催、ここでXeonを中心としたソリューションの紹介や今後の展望などを説明したが、この中で同社のJim Keller氏(Senior VP, GM, Silicon Engineering Group)により2020年までのXeonのラフなロードマップが示された。

内容は、連載464回で紹介した通り、2019年中は引き続き14nmを使った製品が投入されるという話で、新たにCooper Lakeというコアが投入されることが発表された。また今年中(第4四半期なので10月以降)にCascade Lakeが投入されることも発表になっている。

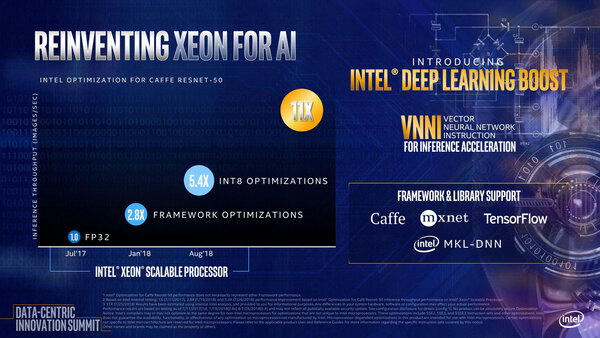

まずCascade Lake、連載253回で触れた時には新たに“Protective walls”(保護障壁)を搭載すると説明したが、これに加えてVNNI(Vector Neural Network Instruction)が追加されている。

これはおそらく、インテルがKnights MillことXeon Phi x205で搭載したAVX512命令の拡張を指すものと思われる。もともとKnights MillはKnights Landingをベースに、AVX512_4FMAPS/AVX512_4VNNI/AVX512_VPOPCNTDQという、DNNの演算に最適化した命令セットを追加することで、DNNのピーク性能をKnights Landing比で2倍にしている。

ほかにもOptane DC(Optane Memoryを搭載したNVDIMM)のサポートや、より高い動作周波数なども相違点として挙げられているが、内部構造に関わる部分ではProtective wallとVNNIの2つのみが差となる。

一方、続くCooper Lakeは新たにbfloat16のサポートが追加されるとする(おそらくAVX512命令への追加であって、x87への追加ではないだろう)。bfloatは連載468回で説明した浮動小数点の話の中には出てこない。

ここで近いのはBinary16(仮数部11bit、指数部5bit)だが、bfloat16の場合は仮数部8bit、指数部8bitになる。つまり、「精度は落としてもいいけど、扱える桁数はFP32(仮数部24bit、指数部8bit)と同じだけ欲しい」というニーズに応えたフォーマットである。これにより、ダイナミックレンジ(=扱える桁)を落とさずに、FP32の倍のスループットで演算が可能になる。

もう1つ興味深いのは、このCooper LakeはIce Lakeとプラットフォームが互換になることだ。逆に言えばCascade Lake→Cooper Lakeではプラットフォームの変更がともなうわけだが、現時点ではこれが単にVRMの仕様が変わる程度の話で済むのか、それともソケットまで変わるのかははっきりしない。ただ2019年のタイムフレームでは、まだメモリーはDDR4のままと思われるので、ソケットまで変える意味が不明である。

かつてのスケジュールではDDR5の標準化は今年中に完了するはずだったが、もう少しずれ込みそうという話が出ている。また仮に今年中に標準化が終わったとしても、2019年中は良くてエンジニアリングサンプルどまり、まともにDDR5の製品が出てくるのは2020年以降になるだろう。

強いて言えばこのCooper Lakeの世代ではI/OがPCI Express Gen4に対応する(公式にサポートするかどうかはともかくとして、PHYそのものはGen4対応の物が入る)のは確実なので、これに合わせてLGA3647v2などにマイナーアップデートが行なわれる可能性はあるかもしれない。

この連載の記事

-

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 - この連載の一覧へ