DDR4とPCIeレーンの構成から推測すると

第2世代Ryzen Threadripperは4ダイ構成のみとなる

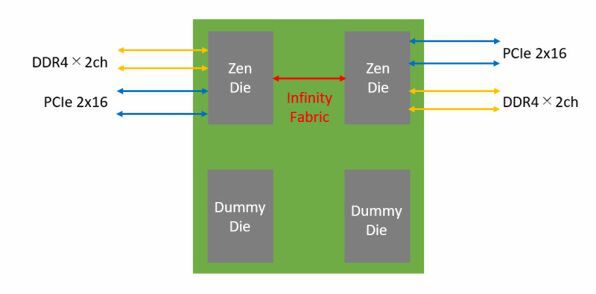

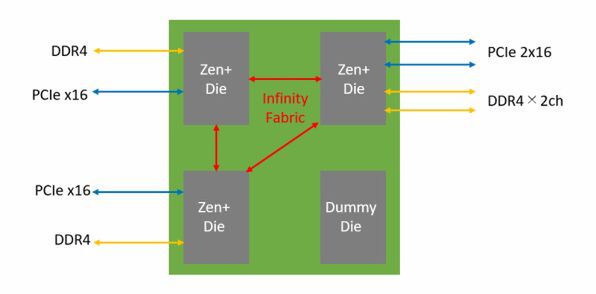

次の話はDDR4とPCIeレーンの構成である。Ryzen Threadripperは下図のような構成になっていた。このRyzen Threadripperと同じSocket TR4ということは、4ダイ構成でもDDR4とPCIe x16レーンはそれぞれ4つのままということになる。

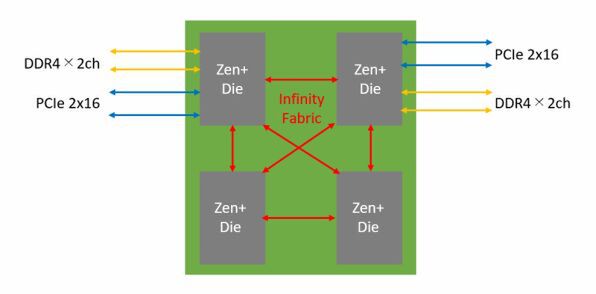

一番簡単なのは下図の構成だ。つまり今までのダミーダイにあたる部分を稼動ダイに切り替え、InfinityFabricでつなぐ方式だ。

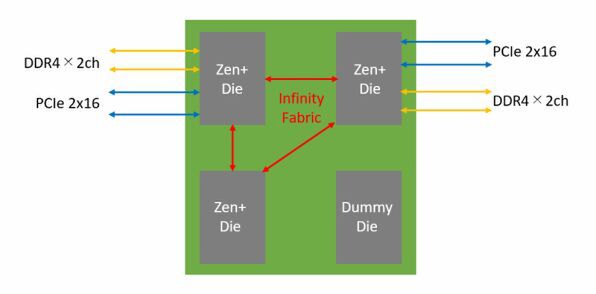

この方式のメリットは、下図のように3ダイ構成にも対応できることだ。一方のデメリットは、どのダイが動くかで極端に性能が変わりかねないことだ。

Zen+でキャッシュやメモリーアクセスのレイテンシーは短縮したが、その一方でInfinityFabric経由の通信は速度/レイテンシーともにほぼ同じであり、つまりローカルメモリー(自分のダイにつながっているメモリー)のアクセスとリモートメモリー(他のダイにつながっているメモリー)とのアクセス性能差がより大きくなった、という意味でもある。

構造的にはNUMA(Non-Unified Memory Access)な以上、ある程度メモリーアクセスの差が出るのは避けられないにしても、どのダイで動くかで性能が大きく変わるとなると、当然高速に動くダイに集中するようなチューニングになってしまうから、せっかく追加したダイの意味がない。

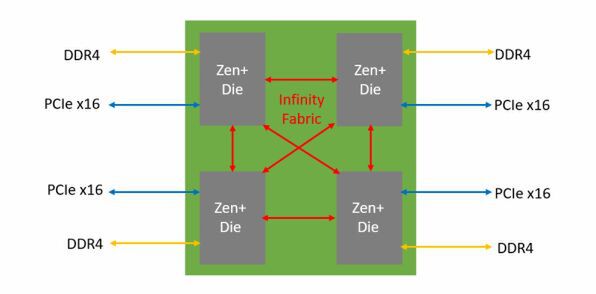

したがって現実問題としては下図のように、4つのダイからそれぞれ1本づつDDR4とPCIe x16が出る形になると思われる。少なくともこれだと、どのダイでもメモリーアクセスやI/Oの性能は均一になるため、チューニングがずっと楽である。

逆に言えば上図の構成をとる場合、3ダイという可能性は皆無ではないにせよかなり低いだろう。無理に3ダイとなると下図のような変な構成にするか、もしくはDDR4とPCIeが3本づつ有効という制限付きになってしまい、明らかに既存のRyzen Threadripperより性能が落ちるシーンが出てくることになりかねない。

したがって、4ダイ構成のみになるだろうというのが筆者の現時点での予測である。

この連載の記事

-

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 -

第847回

PC

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手 -

第846回

PC

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ - この連載の一覧へ