AMDは5月16日(日本では5月17日の午前5時)、投資家向けとなるFinancial Analyst Dayを開催し、この内容をウェブキャストで全世界に配信した。ここで新製品の話が出てきたので、分野別にまとめて解説しよう。

サーバー向けCPU“EPYC”は

4ダイ構成のMCM

連載400回で解説したZenコアベースのNaplesであるが、このブランド名が“EPYC”(エピック)になったと、CEOのLisa Su氏より明らかにされた。

このEPYCとRadeon Instinctでサーバー市場に殴り込みをかけよう、というのがAMDのサーバーに向けた基本戦略である。

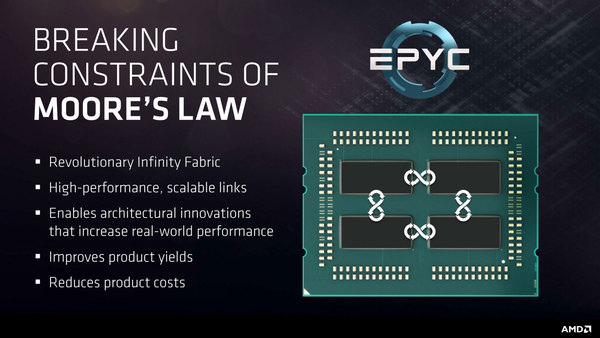

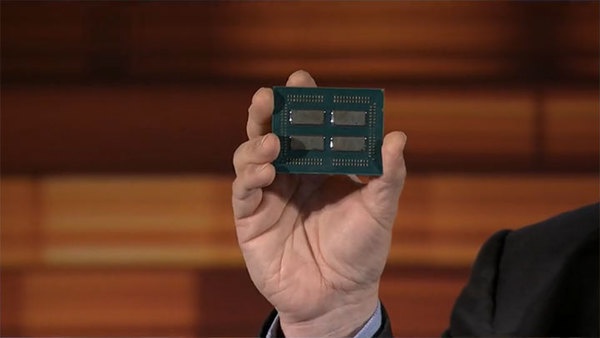

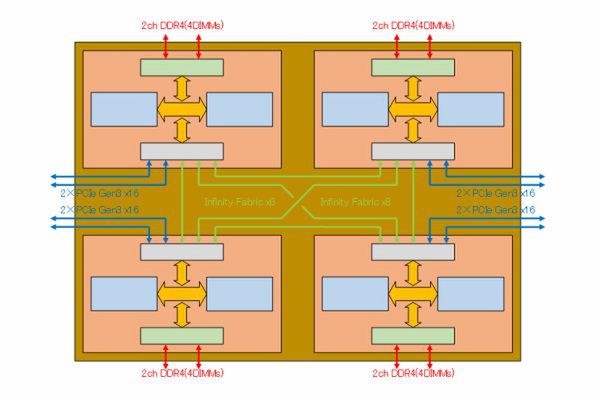

さてそのEPYCであるが、やはり想像通り4ダイ構成のMCM(Multi-Chip Module)であることが明らかにされた。パッケージを見る限りはシリコンインターポーザーは使わない、ただのMCMである。

筆者の推測が正しければダイの間はそれぞれx8程度のInfinity Fabricで接続されるだけで、後はDDR4、PCIe、それと電源/GNDだけで、HBM(High Bandwidth Memory)のような高速かつバス幅の広いI/Fは使わないため、MCMを利用する必要はないのだろう。

気になるのは、IO Hubに当たるチップが見当たらないことである。あるいはIOハブのみ裏面あるいはパッケージ内配線なのだろうか?

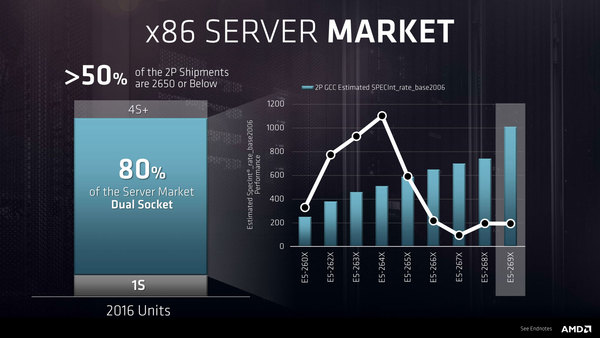

さて、ここからは市場と性能比較の話である。2016年の場合、サーバー市場全体の80%は2ソケット構成となっている。ただ右のグラフを見るとわかるが、性能はもちろんハイエンドの「Xeon E5-269X」が一番高いのだが、出荷量が一番多いのは「E5-264X」、次いで「E5-263X」、「E5-262X」、「E5-265X」という順で並んでおり、要するに出荷量の大半はそれほどコア数の多くないMCC(Mid Core Count)/LCC(Low Core Count)製品に集中しているとする。

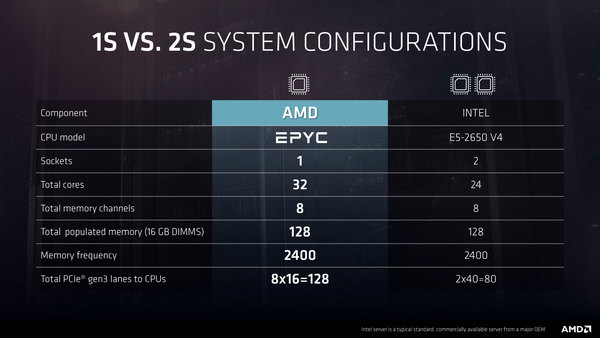

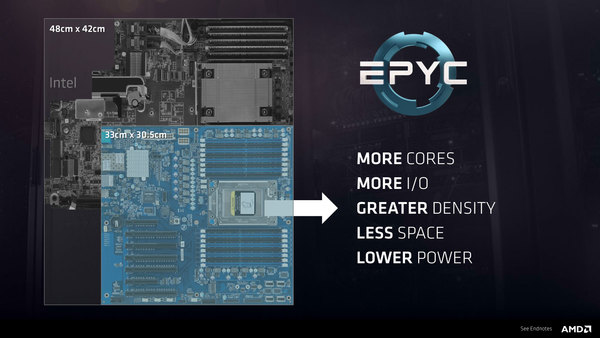

これを前提に、ライブデモとして「Xeon E5-2650 V4」の2ソケット製品 vs. EPYCの1ソケット製品のベンチマークが行なわれた。デモは8つのVMを立ち上げるというものだが、EPYCの方が早く立ち上げられる、という結果が示された。この1P EPYCのボードも今回紹介されている。

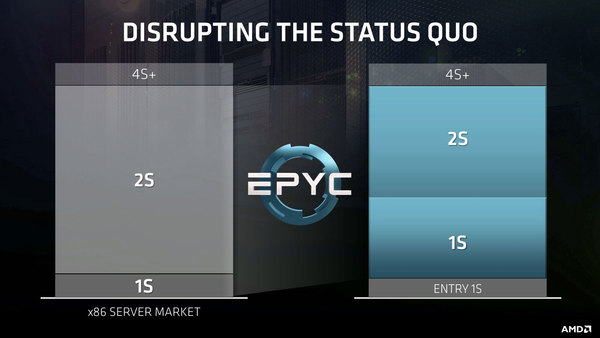

AMDはこれまでボリュームゾーンとして大量に出荷されていたローエンドの2ソケットサーバーを、このEPYC 1Pで置き換えられるとアピールしており、現在のXeon 2ソケットの市場の下側はEPYC 1ソケット、上側をEPYC 2ソケットでカバーできる、としている。

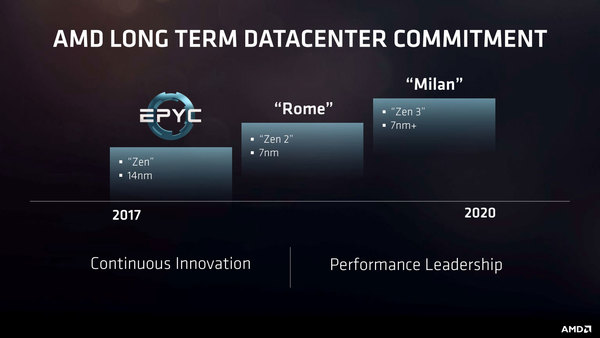

最後にロードマップであるが、現在のEYPCは14nmのZenコアベースであるが、これに続いて7nm世代のZen 2、そして7nm+世代のZen 3がそれぞれRome/Milanとして投入される予定になっていることが今回明らかにされた。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ