SUPERNUMを変形させたような構成の

GENESIS

そのGENESIS、正確にはGENESIS Version 1のノード構成は下の画像のようになった。1つのノードにCP(Communication Processor)とAP(Application Processor)の2つのi860XPが搭載され、両者はLCI(Local Communication Interface)という専用バスで接続される。

名前の通り計算処理はAPが担い、CPがノード間通信を担うという仕組みだ。NLIはNetwork Link Interfaceでノード間接続を行なう。

また2つのi860XPは共有メモリーバス経由で8MB×4Bank=32MBのメモリーを利用できる。860XPそのものは共有メモリーI/Fなどは持ち合わせていないので、これはGENESIS側で設計・製造したと思われる。

メモリーI/Fは3段のパイプライン構造で、帯域は最大320MB/秒になるとされる。100MFLOPSということは倍精度では理論上800MB秒の帯域が必要になるが、さすがにそこまでは用意できなかったらしい。

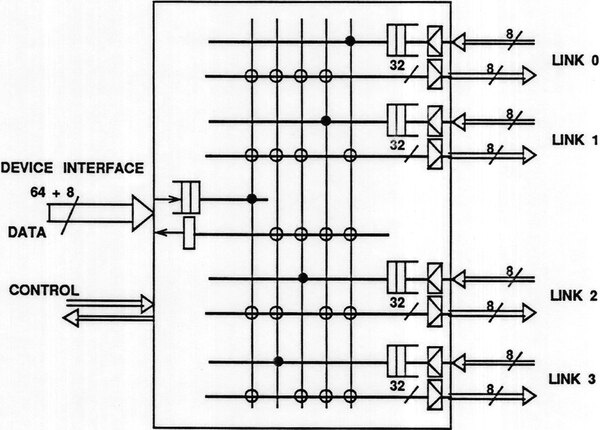

このノードのCPにつながるNLIの構造が下の画像である。1つのノードからクロスバスイッチ経由で4本のリンクが出る仕組みになっている。リンク速度は当初は1本あたり50MB/秒とされる。

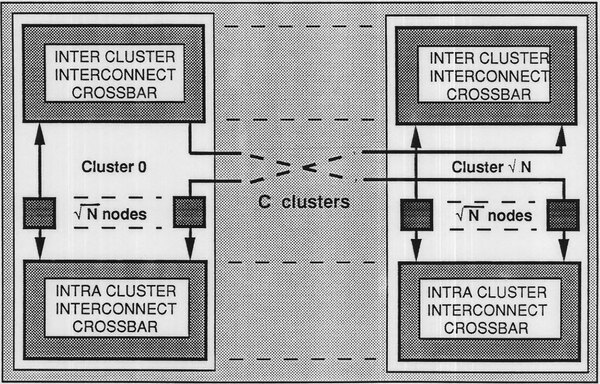

問題はリンクがノードあたり4本しか出せないことである。1024ノードをターゲットとする場合、HyperCube構造を取るならノードあたり10対20本のリンクを用意する必要があるが、さすがにこれを構成するのはコスト面から非現実的と判断された。

そこでGENESISではSUPERNUMを変形させたような構成とした。まず少数のノードをクロスバスイッチでつなぎ、小さなクラスターを構成。このクラスター同士をさらにインターコネクトでつなぐという2段階の接続方式が採用された。

具体的な数字が出てこないのだが、おそらく1クラスターを32ノード構成とし、このクラスターを32個つないで1024ノードを実現する予定だったと思われる。

1つのクラスターには2つのInter-Cluster Crossbarが含まれており、うち1つはクラスター内のノードの接続に、もう1つはクラスター間の接続に利用する方式だ。

ベクトルプロセッサーを追加して

性能向上を計画したVersion 2

ここまでで100GFLOPSのマシンを構築できるメドは立ったことになる。SUPRENUM-1が理論性能で5.12GFLOPSだったから20倍の高速化であるが、さらに性能を上げたVersion 2も予定されていた。

どうやるかというと、これまたSUPRENUM-1と似た、ベクトルFPUの搭載である。下の画像がそのVersion 2でのノード構成だが、新たにベクトルプロセッサーを追加してもう一段ノード性能を上げようというわけだ。

このベクトルプロセッサー、採用を考えていたのはBIT(Bipolar Integrated Technology)の提供していたB2110/2120である。

WeitekのFPU同様、B2110が32bitの加算、B2120が32bitの乗算を実行するチップで、この2つを組み合わせて乗加算をスループット1サイクルで実行できた。

B2110/2120を使う場合、さらにB2210というSRAMのレジスターファイルも組み合わせる必要があるので、おそらく搭載される予定だったと思うのだが、さすがにそこまでははっきりしない。

このBITという会社、名前の通りバイポーラベースのFPUを作っている会社で、B2110/2120は同社の初の製品である。ちなみに会社は1983年にオレゴンで設立されたが、設立資金を出したのがFPSとインテル、それにTektronixというあたりからも製品の方向性が見えようというものだ。

その後同社はECLベースのSPARCチップや、ECLベースのMIPS R6000など、とにかく動作周波数を引き上げること「だけ」に専念した製品をいくつかリリースするが、半端ない消費電力もあって商業的には成功せず、最終的に1996年にPMC-Sierraに買収されてしまう。

そのB2110/2120だが、1990年の段階ですでに33MHz動作のチップは存在しており、かつこれを利用したベンチマークソフトも走っていたらしい。同社はB2110/2120を最終的に100MHz以上まで動作周波数を引き上げる計画をこの時点で発表していた。

上の画像のVersion 2のノード構成でもわかるように、このB2110/2120を利用してベクトル長4のベクトルプロセッサーを構築することで、理論上は400MFLOPSが実現できるはずで、これを全ノードに搭載すれば400GFLOPSのマシンができあがる計算になる。なかなか気宇壮大な話である。

→次のページヘ続く (ソフトウェア開発に専念)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ