前回はZシリーズの系列を解説したので、今週はPOWERシリーズの系列を解説しよう。といっても、POWERシリーズはこれまでもいくつか説明している。

そもそもPOWERプロセッサーが生まれるまでの経緯(ROMPからPOWER1への移行)は連載494回で触れているほか、そのPOWER1→POWER2への変遷は連載289回のASCI Blueで、POWER3は連載290回のASCI Whiteで、POWER4→POWER5は連載293回のASC Purpleでそれぞれ説明している。

簡単にまとめれば、以下の変遷を辿っている。

| POWERプロセッサーの変遷 | ||||||

|---|---|---|---|---|---|---|

| POWER1 | POWERアーキテクチャ元祖 | |||||

| POWER2 | スーパースカラー搭載、ワンチップ化 | |||||

| POWER3 | Out-of-Order搭載、実行ユニット強化、SMP対応 | |||||

| POWER4 | スーパーパイプライン化による高速動作、MCMによる8P構成 | |||||

| POWER5 | SMT搭載 | |||||

スーパーパイプラインで高速化した

POWER4とPOWER5

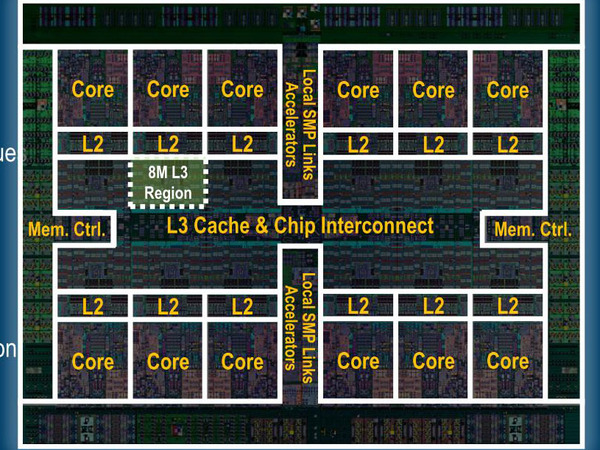

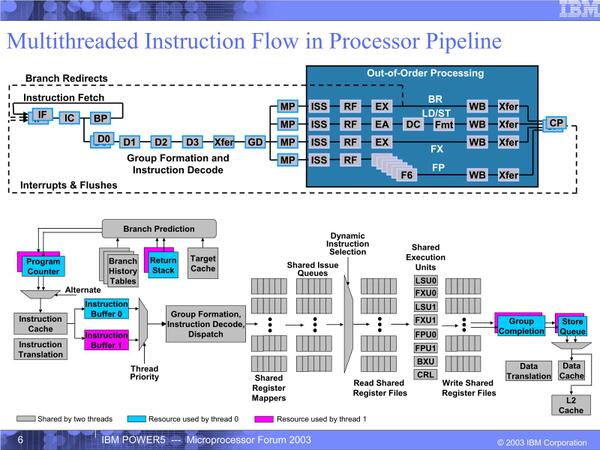

そのPOWER4/POWER5のパイプライン構造は下の画像のような構成である。POWER4は2命令同時解釈、4命令同時発行で、POWER 5はこれが2命令同時解釈、8命令同時発行に強化されてはいるが、パイプライン段数は整数演算14段、FPU演算17段で、これはPOWER5にも継承された。

画像の出典は、MicroProcessor Forum 2003におけるBalaram Sinharoy博士(POWER5 Chief Scientist, IBM Systems Group)の“IBM POWER5 Systems”

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ