製品発売前に対応プロセッサーが生産中止

さて、OSを作るにあたっては当然ながら想定されるハードウェアがなにかないといけないのだが、当時のマシンの中でGassee氏のお眼鏡にかなう物はなかったらしい。そこで当初、同社はAT&TのHobbitというプロセッサーを使って最初の開発ボードを構築する。

AT&TのHobbitはCRISP(C-language Reduced Instruction Set Processor)というアーキテクチャーに基づくものである。このCRISP、もともとはAT&T傘下のベル研究所で1980年代に研究されていた、“C Machine”(C言語で記述されたプログラムを高速に実行するプロセッサー)のプロジェクトの産物である。

CRISPチップのうち、C言語の解釈部分を手がけたのはDavid Ditzel氏、この後SPARCやAm29000の設計を手がけTransmetaを立ち上げる、あのDitzel氏である。HobbitはこのCRISPチップの商用版という位置づけになる。

パイプライン構造は3段で、命令は1/2.5/3バイトの可変長(このあたりはRISCっぽくない)、ほとんどの命令は1サイクルで実行可能、かつ分岐予測をディレイなしで実行可能で、投機実行すら可能になっていた。

命令プリフェッチバッファー(事実上のL1 I-Cache)は当初の92010が3KB、後継の92020が6KBであり、20MHz駆動の92010は12 DMIPS(Dhrystone MIPS)(13 DMIPSという数字もある)を叩き出している。製造は0.9μmプロセスのCMOSで、性能/消費電力比はかなり高かったが、絶対性能はそうでもなかった。

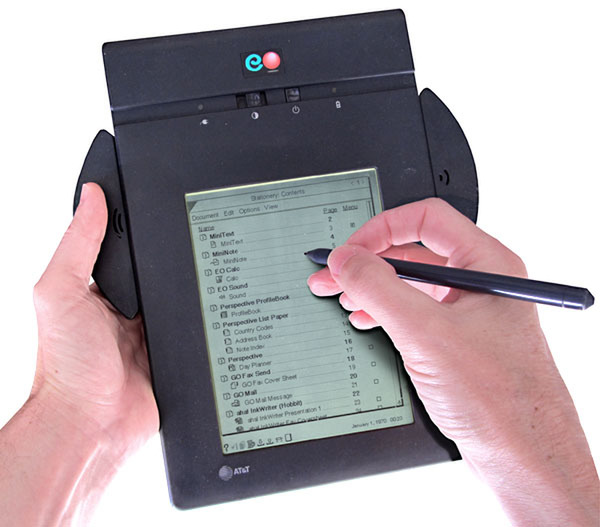

AT&TはこのHobbitをARMのプロセッサー(Newtonに採用されたARM 610を競合と位置づけていた)に代わり、PDA市場でシェアを取れることを期待し、自社でもGo ComputingのPenPointを搭載したEO-440 Personal Computing Systemを開発して、1992年のCOMDEXでお披露目した。

画像の出典は、“oldcomputers.net”

ちなみにこのCOMDEXにおける発表の17時間前に、日本でもEO-440の発表会が開催された「らしい」が、これを裏付ける発表会レポートはすでにどこにも残っていない。

話は錯綜するのだが、もともとこのEO-440を開発したEO Personal Communicatorという会社はGo Computingからの独立組で構成されていた。1992年にAT&Tに買収されて、EO-440はAT&Tからの発売になるのだが、実はEO-440の発売以前にAT&Tの半導体部門はHobbitの生産中止を決めていたらしい。

要するにNewton向けプロセッサーの座をARM 610に奪われたため、市場性に欠けると判断したらしいのだが、その話はEO-440の部隊にまったく伝わっていなかったらしい。

ついでに言えば、AT&TはこのEO-440を家庭向けに開発・発売したわけだが、それとは別にAT&Tは業務向けにGeneral Magicと組み、Telescriptと呼ばれる手書き入力サービスをベースにしたシステムを構築し、これをプロバイダーに提供するビジネスも並行で動いていた。

要するにAT&Tと一口で言っても隣の部隊がなにをやってるかさっぱりわからない状態だったらしい。そんなわけでEO-440も発売はしたものの、肝心のCPUが生産中止とあれば売れるわけもなく、結局ひっそりと消えていった。

ようやくハードウェアが完成

BeOSが実装される

だいぶ脇道に逸れたので話を戻そう。1990年といえばまだこのHobbitチップの売り先をAT&Tが模索していた状態であり、Beにとっては都合が良かったのかもしれない。最初のBeOSはHobbitをベースに実装されることになる。

ただ12(13) DMIPSはPDAには十分でもPCには明らかに非力である。なにせインテルは1989年に80486DX/50MHzをリリースしており、明らかに見劣りした。66MHzのものが54 DMIPSなので50MHzでは41 DMIPSほどになるからだ。

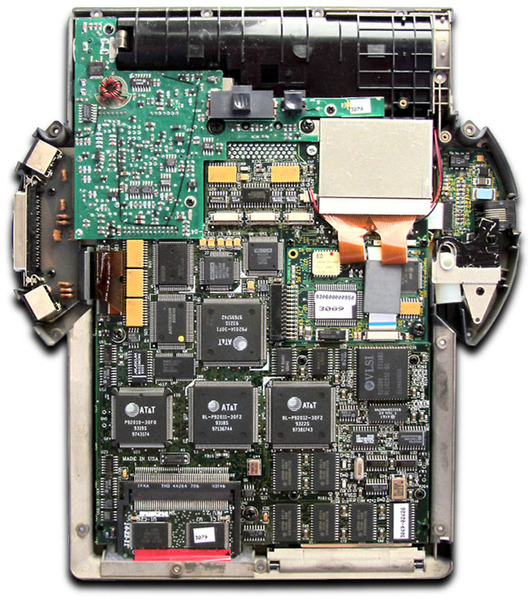

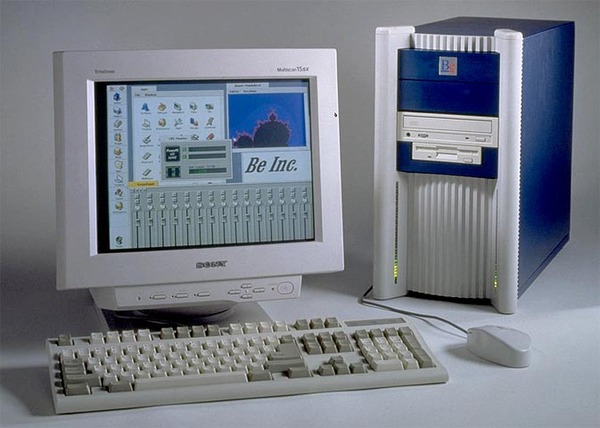

そこでBeは途中でターゲットをHobbitからPowerPCに移行させ、1995年にBeBoxとして発表する。Hobbitベースの開発ボードの構成はHobbit×2とAT&D 9308S DSP×3というものだったが、これが66MHz/133MHzのPower PC603×2に切り替わった。

画像の出典は、“old-computers.com”

メモリーはSIMMスロット×8で最大256MB、PCIスロット×3、ISAスロット×5、オンボードでSCSIとIDEポートを持つほか、シリアル×4、PS/2マウス、ジョイスティック×2、MIDI In/Out各2、IRポート×3、オーディオ入出力×2、さらにGeekPortと呼ばれる独自の拡張ポートも搭載されるという、なかなかに重厚な構成である。

1995年10月に発表されたのはPowerPC 603 66MHz×2の構成で、価格は1600ドル(基本構成)。翌1996年8月にはプロセッサーをPowerPC 603 133MHz×2に強化したものが、2995ドルで発売された。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ