前回のスーパーコンピューターの系譜では、BlueGene/Lの解説をした。今回はその続きである。

BlueGene/Lの後継機「BlueGene/P」

連載299回の冒頭でも御紹介したが、Protein Folding(タンパク質の構造解析)のシミュレーションのためには1PFLOPSの性能が必要とされた。

一足飛びにこれを実現するのは難しいということで、当初は100TFLOPS級(実際は300TFLOPS)のBlueGene/Lをまず完成させたわけだが、この後継として、いよいよ1PFLOPSを狙うBlueGene/Pが設計されることになった。

ちなみにBlueGene/Pが完成したと発表されたのは2007年6月のこと(関連リンク)で、BlueGene/Lの発表からおよそ3年半後ということになる。ゼロから完全にアーキテクチャーを作り直したわけではないことを考えれば、妥当な数字だろう。

BlueGene/L比で2.4倍ほどの性能を実現した

BlueGene/P

そのBlueGene/Pは、基本的にはBlueGene/Lの発展拡張型である。どう発展拡張させたかというと下表のとおりである。

| BlueGene/LからBlueGene/Pへの発展 | ||||||

|---|---|---|---|---|---|---|

| CPUコア | PowerPC 440→PowerPC 450へ | |||||

| FPU | 4 FLOPS/サイクルのまま | |||||

| 動作周波数 | 700MHz→850MHzへ | |||||

| コア数 | 2コア/チップ→4コア/チップへ | |||||

| コンピュートカード | 2チップ/カードから1チップ/カードへ | |||||

| ラック | 32ノード/ラックのまま | |||||

| システム | 64ラックから72ラックへ | |||||

コア数は増えたものの、コンピュートカードあたりのコア数は4つになるので、ここの差はない。しかしノードカードあたりの密度は2倍になり、さらに動作周波数を若干引き上げたことで、BlueGene/L比で2.4倍ほどの性能を実現したことになる。

もう少し細かく説明しよう。まずPowerPC 450というコアである。このコアは事実上BlueGene/P専用といっていい。

PowerPC 440は汎用の組込み向けコアであり、IBM以外にもAMCC(現APM)などが製品をリリースしていた。この後継がPowerPC 460で、こちらはPowerPC 440にDSP命令を追加したような構成である。

パイプライン構造などはPowerPC 440と大きくは変わらないが、プロセス微細化などで1.4GHz駆動が可能になっている。

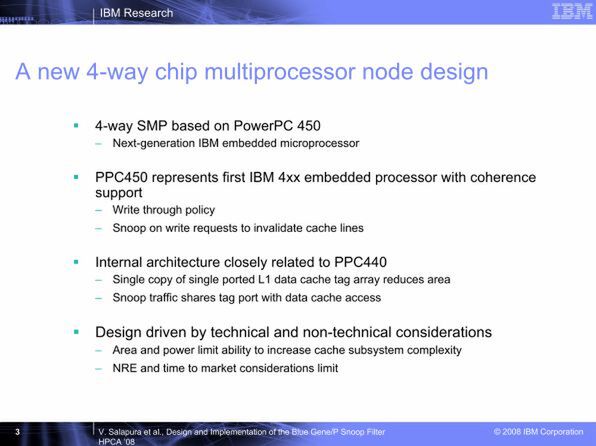

ではPowerPC 450はなにかというと、IBMは下の画像で説明している。元々PowerPC 440はシングルコアの製品なので、マルチプロセッサー構成は考慮しておらず、これをカバーするためにコアの外に小容量の2次キャッシュを搭載、ここでキャッシュスヌープを実装する形にした。

具体的には、1次キャッシュにキャッシュコヒーレンシーの機構が搭載されている。逆に言えば他の部分はあまり変わっていない。これは“デザインに関する技術/非技術的な配慮”として以下の2点が挙げられる。

- キャッシュサブシステムは、ダイエリアおよび消費電力の制限により複雑さが抑えられる

- 初期コスト(NRE)及びマーケット出荷までの時期の制約がある

このうちの2点目は、Blue Geneプロジェクトが元々はIBMの単独プロジェクトであることと関係する。ASCI/ASC系列の場合、エネルギー省などの政府機関から開発コストが支払われるため、内部アーキテクチャーを大幅に変える、つまり開発コストが跳ね上がることも場合によっては許容されるが、Blue GeneはIBM社内のプロジェクトなので、余分なコストはかけられない。

その結果、CPUパイプラインそのものはPowerPC 440からほとんど変更がないようだ。「ようだ」と書いたのは、IBM自身がこのPowerPC 450についてはこれ以上の詳細な説明をしていないからでもある。

ちなみにこのPowerPC 450には派生型としてPowerPC 450dというコアもあるようだが、違いは不明である。

そもそもBlueGene/PしかPowerPC 450を使っていない状況でなぜ2種類のコアがあるのかもよくわからないが、あるいはBlueGene/Pの生産の前期型と後期型で少しコアに手が入ったのかもしれない。

また、BlueGene/Lと同じく外付けでDouble PumpのFPUが搭載されている。このFPUはBlueGene/LのDouble-Hammer FPUと構成そのものは同じで、単に製造プロセスが微細化されただけのようだ。

→次のページヘ続く (速度を大幅に高速化したBlueGene/Pの構造)

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ