CPU黒歴史AMD編の第4弾は「Barcelona」こと、初代「K10」の話をしたい。正式な開発コード名はともかく、発表当時は社内外でこのK10ベース「Opteron」の開発コード名であるBarcelonaが広く使われていたので、本稿でもこのBarcelonaを使って話を進めよう。

多くの改良を取りこんだBarcelona

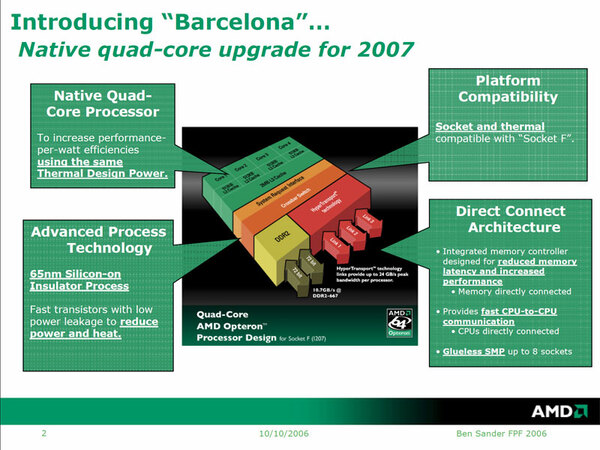

Barcelonaという名前、そして細かな内部構造が初めて発表になったのは、2006年10月に開催された「Micro Processor Forum 2006」だったと記憶している。この時はAMDのベン・サンダー氏(Ben Sander、Principal Member of Technical Staff)が説明しており、その後同じ内容が2006年末に開催されたアナリスト向けミーティング「AMD Day 2006」でも発表されている。

この時点でのBarcelonaの主な特徴は、既存のK8コア(Athlon 64 X2)をベースに同じ65nm SOIプロセスを使いながら、以下の項目が改善点として挙げられた。

- ネイティブ・クアッドコア化

- IPCを改善

- 128bit SSE動作をサポート

- メモリー帯域を拡張

- 3次キャッシュを搭載

- 仮想化支援機能の搭載

- 電源管理機能を拡充

IPCに関する最大の目玉は、命令フェッチを最大32Byte/サイクルに広げたことである。ほかにもIPCについては、「Sideband Stack Optimizer」(後述)などいろいろな項目が並んでいる。

Sideband Stack Managerとは、インテルが「Dedicated Stack Manager」という名前でPentium Mから搭載したものとほぼ同じ機能で、PUSH/POPというレジスターの退避/復帰命令を、ALUを使わずに処理する機能である。IPCに関するそのほかの改良点は、おおむね既存の回路の改良といったところ。個々の要素が大きくIPCを引き上げるわけではないが、全体を組み合わせることでIPCの改善がある程度実現される、という話であった。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ