NECは、ベクトル型スーパーコンピュータ「SX-Aurora TSUBASA」を活用したアニーリングマシンサービスを、2020年第1四半期から開始すると発表した。さらに、量子コンピューティング推進室を2020年1月に設置し、顧客との共同実証を通じた用途開発および技術開発を推進。人材育成も行なう。また、D-Waveとの協業検討についても明確化するとともに、2023年に量子アニーリングマシンの実用化を目指す考えも明らかにした。

ベクトル型スーパーコンピュータ「SX-Aurora TSUBASA」を活用したアニーリングマシンのサービスを提供

増え続ける組み合わせ最適化問題にも迅速に対応

新サービスで活用するSX-Aurora TSUBASAは、卓上型スーパーコンピュータといえるもので、NECでは、これを活用した共創サービスと位置づけている。新たに開発したシミュレーテッド・アニーリングマシンの活用が可能であり、組み合わせ最適化問題を解決するために、アニーリング処理に適した独自開発のアルゴリズムを組み込んだソフトウェアと、ベクトルコンピュータを組み合わせた超高速処理を可能にした。

NEC 取締役 執行役員常務兼CTOの西原基夫氏は、「10万量子ビット相当の大規模な組み合わせ最適化問題に対応できる。金融ポートフォリオや人員シフト計画、工場生産計画、創薬などで効果を発揮するだろう」とした。また、ビッグデータやAIとの連携が容易であり、NEC社内での活用では、従来のシミュレーテッド・アニーリングマシンに比べて、300倍以上高速に計測できることが確認できたという。

NEC 取締役 執行役員常務兼CTOの西原基夫氏

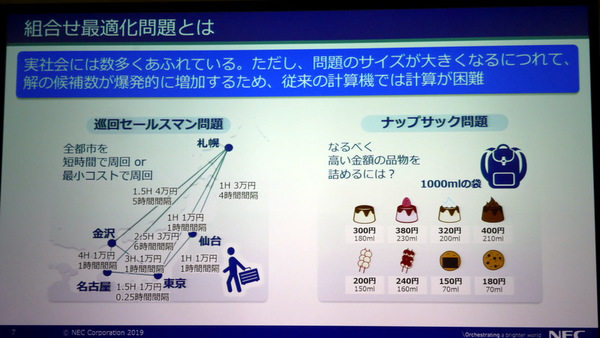

「組み合わせて最適化問題は、社会には数多くあふれているが、問題のサイズが大きくなるにつれて、解の候補数が爆発的に増加するため、従来のコンピュータでは計算が困難であった。しかし、量子コンピュータでは、これまでのコンピューティングでは不可能であった問題を解決できる。たとえば、期待する薬効を発揮する化合物の探索や試薬の試行錯誤を通じて新たな薬の開発に活用したり、金融商品においては、儲かる組み合わせを発見し、顧客にアドバイスするといった使い方が可能になる。個人ごとに理想的な特効薬を作ったり、最適な経路誘導を算出したり、人と人、人や仕事をマッチングするような気がつくことができる新たな街づくりに生かしたり、製造業では個別に最適な製品サービスの提供などにつなげることができる」とした。

現在、NECでも関連会社工場において、生産計画立案に活用。使用部品や設備設定などの違いから、製品により異なる段取り時間を最小化するために、基板の表面実装工程の現場データを活用して、膨大な組み合わせ計算を実行。6時間あった段取り替えに伴う生産ラインの停止時間を最大で30%減少させることに成功したほか、計画立案時間も数時間かかっていたものを数秒で完了させたという。

だが、その一方で、「量子コンピュータには得意不得意があり、単一のコンピューティング技術ですべての問題を解くことはできない。たとえば、津波の発生時には、スーパーコンピュータで津波被害の事前シミュレーションを行ない、リアルタイムでの避難経路を最適化については量子コンピュータで解き、GPUを活用した画像処理による避難者などの群衆行動検知を行なうといった使い分けが最適だと考えている」などと述べた。

また、新設する量子コンピューティング推進室は、顧客との共同実証を通じた用途開発および技術開発を推進するもので、「約20人体制でスタート。既存技術とAIの活用技術を検討していくことになる。顧客のビジネス課題の抽出と問題設定を行ない、問題の定式化や重点分野における検証を行なうことになる。重点領域として、金融系、創薬系、物流系、大規模社会システム運用などを想定している。量子コンピューティングを推進する司令塔の役割を担う」などとした。

一方、D-Waveとの協業検討に関しては、「D-Waveが持つ200以上のアプリケーションを試用でき、ユーザーニーズーの把握、検証や教育などのサービスの提供を加速のほか、ソフトウェアやアプリケーションの開発を加速できる。NECの量子コンピュータの取り組みにおいては、大きなステップになり、今後の展開において重要なパートナーになる」と述べた。

2023年に量子アニーリングマシンの実用を目指す

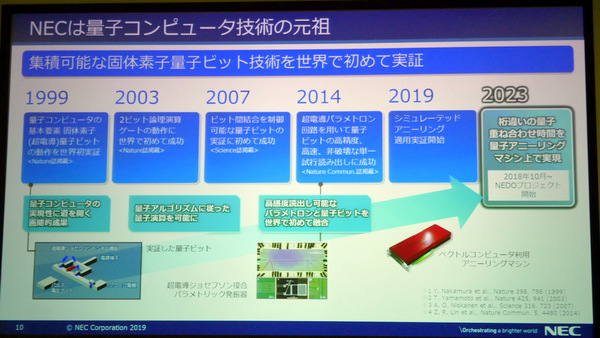

NECは、1999年に超伝導固体素子を用いた量子ビットの動作実証に世界で初めて成功。その後、量子ビットや量子状態を制御するデバイスや回路の研究を進めてきた。2003年には2ビット論理演算ゲートの動作に世界で初めて成功。2007年にはビット間結合を制御可能な量子ビットの実証に成功。2014年には超電動パラメトロン回路を用いて、量子ビットの高精度、高速、非破壊な単一試行読み出しに成功しており、パラメトロンと量子ビットを世界で初めて融合した。

2018年10月からは、国立研究開発法人 新エネルギー・産業技術総合開発機構による新規事業「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/次世代コンピューティング技術の開発」において、4量子ビットの基本量子セルの動作を検証中である。

「NECが採用している超電動量子パラメトロン方式は、多ビットでもノイズに強いため、2~3桁長い量子状態を保つことができ、まさに桁違いの量子計算時間を実現できる。さらに、4物理量子ビットの基本構成を繰り返す方式との親和性が高く、全結合でのスケール化が容易である」(西原氏)

NECは、4物理量子ビットを基本単位として、全結合の論理量子ビットを構築する技術を採用しているため、この動作検証が確立すると、基本量子セルの繰り返し配置により、全結合での多ビット化につながり、これがスケールアウトへの重要な一歩になるとしている。

「2023年に量子アニーリングマシンの実用化を目指す。リアルタイム性が重要な領域に活用できる。無線ネットワークの最適化や自動制御系などでの利用を想定している。求解時間と規模にトレードオフの関係があるため、量子アニーリングマシンと、ベクトルコンピュータによるシミュレーテッド・アニーリングマシンを適材適所に活用していくことになる」(西原氏)

2023年に実用化を目指す量子アニーリングマシンのモックアップ