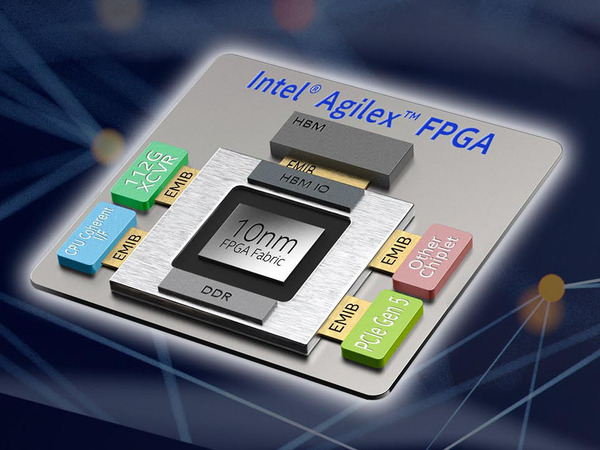

ひさびさにインテルのロードマップをお届けしよう。4月2日にData-Centric Innovation Dayがサンフランシスコで開催され、ここで第2世代のXeon ScalableプロセッサーやOptane MemoryベースのPersistent MemoryというSSDが正式発表されたほか、10nmプロセスのFalcon MesaことAgilex FPGAなどが発表された。

これらは基本的にはクライアント側にはあまり関係ない話題であるが(おそらくクライアント側の発表は例年通りCOMPUTEXとなるはずだ)、このイベントの前にいくつか興味深い発表があったので、まずはそれを順次説明していきたい。

10nmプロセスは先に進みすぎた

インテルのSenior Fellowとして長年プロセス部門を統括していたMark Bohr氏が65歳になり、今年3月に引退された(すでにBiographyのページは削除されている)。その引退一ヵ月前の2019年2月に、OregonLiveがインタビューを行なった記事が掲載されているが、興味深い発言があった。引用すると

“We kind of overshot, I think, on our 10nm technology,”

“We bit off a little too much at that step,”

“Maybe we should have relaxed a bit in our goals and it would have been a much easier transition.”

としている。ラフに訳せば以下のようになる。

「10nmプロセスで、我々は少しやりすぎた。」

「ちょっとだけ、先に進みすぎた。」

「目標をやや緩める必要があるだろうし、そうすれば容易に実現できるだろう。」

筆者は連載483回でハイパースケーリング路線の放棄を予想したが、これを追認するような談話が出てきてちょっとほっとしている。単に予想が当たった、というだけでなく10nmプロセスをが正常化されそうな見込みが見えてきそうだからだ。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ