約1年近く続けてきたスーパーコンピューターの系譜。その最後として今回はFPGAを解説したい。

古くはCCC(Cray Computer Corporation)の閉鎖後に設立されたSRC Computersが、FPGAをベースとした製品をリリースしていた(現在もしている)し、CRAYも一時期XD1をリリースしていた。

昨今はマイクロソフトがデータセンターでFPGAを使っていたという話もあり、実はデータセンター向けのニーズが徐々に増えつつある。このFPGAについては連載307回でさらっと解説しているが、もう少し細かく説明しよう。

あらゆる回路を構成できる反面

ICを複雑につなぐ必要がある

FPGAはField Programmable Gate Arrayの略である。“Field Programmable”が肝で、つまり製造後に内部のロジックを書き換え可能なゲートアレイという意味となる。もちろん、これでは意味がわかりにくいだろう。

そもそもデジタル回路はすべて0か1の2値で表現される、という話は連載237回で紹介した。

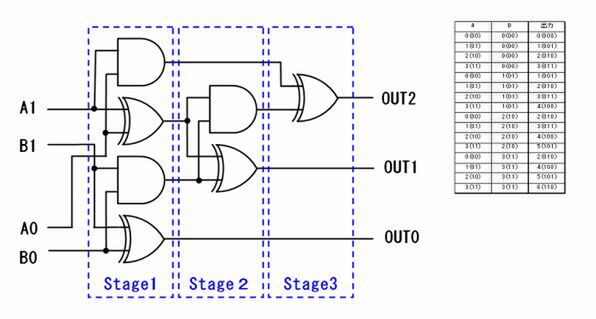

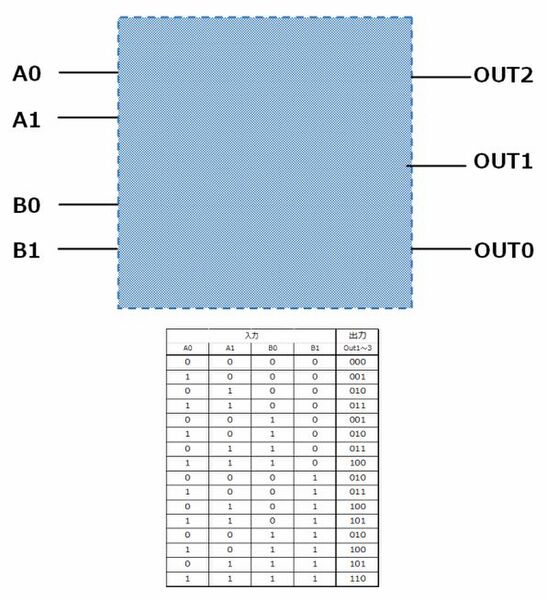

連載237回では2bitの加算器(Adder)回路を解説したが、全体を「入力が4bit(A0/A1/B0/B1)、出力が3bit(OUT 0/1/2)の箱」とみなすこともできる。

したがって、図2のように、4bitの入力と3bitの出力の組み合わせが図1とまったく同じ別の回路を構成すれば、それは図1の回路と置き換えて2bitの加算器(Adder)と称することができる。ここまでは普通の話だ。

当初、真空管やトランジスタベースだったデジタル回路は、TI(Texas Instruments)の7400シリーズや、その後継の標準ロジックICをベースに構成できるようになった。

この7400シリーズはものすごく多い(Wikipediaに一覧がある)ため、これを組み合わせれば複雑な回路も構成できる一方、標準ロジックに含まれていない回路を組みたい場合、標準ロジックICを複数個、複雑につなぐ必要があり、これが面倒だった。

そこで、回路を自由に構成できるICがほしい、という希望は昔から多くの人が抱いていた。これを最初に実現したのがPLD(Programmable Logic Device)である。

製品としてはMonolithic Memories, Inc.(1987年にAMDに買収され、その後Vantisとしてスピンアウト後、Lattice Semiconductorに買収された)がリリースしたPAL(Programmable Array Logic)が最初のものとなる。

この連載の記事

-

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 - この連載の一覧へ