インテルCPUの進化を辿る企画。今回は「Merom」こと「Core 2」プロセッサーに搭載された「Coreマイクロアーキテクチャー」について解説しよう。

Yonahをベースに同時4命令実行に対応

Coreマイクロアーキテクチャーは基本的に、前回解説した「Yonah」からの正常進化、という範疇ではあるが、いくつかの要素も変更した結果として、この世代は機能と性能の両面で大幅な進化を遂げている。それもあってか、Yonahまでは特に明確な名前が付けられていなかった内部アーキテクチャーに対して、Coreマイクロアーキテクチャーという名前をわざわざ付けてアピールしている。

これはむしろ「NetBurstアーキテクチャーからの切り替え」を明確にするため、という意味があるのかもしれない。Pentium 4の世代、インテルは内部アーキテクチャーにNetBurstアーキテクチャーという名称を付けてアピールをしていた。この「アーキテクチャー名のアピール」をPentium 4でやり過ぎたがゆえに、Pentium 4から切り替えるにあたって、新しいアーキテクチャー名を強くアピールしないといけなくなったというあたりが、Coreマイクロアーキテクチャーなる名前が表に出てきた理由ではないかという気がする。

実際、Core 2以降は正常進化ということもあって、「Nehalemマイクロアーキテクチャー」や「Sandy Bridgeマイクロアーキテクチャー」といった具合に、インテルは開発モデル名でマイクロアーキテクチャーを紹介しており、こうした名前は付いていないことからもこれが伺える。

それはともかく、YonahからMeromへのアーキテクチャー変更では、以下の3点が主な違いとなる。

- 同時4命令実行にパイプラインを強化

- EM64Tに対応

- Macro Fusion(旧称Macro Ops Fusion)を実装

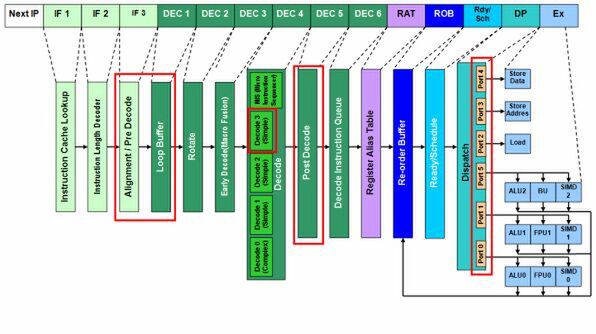

Coreマイクロアーキテクチャー最大の変更点は、同時4命令実行を実現したことだ。これはパイプラインのフロントエンドほぼ全体に影響を及ぼすことになった。「IF1」から「IF3」までのフェッチステージは、おおむねYonahと同じものだ。

ただし、128bit幅のバス(=16byte/サイクル)で1次命令キャッシュから命令をフェッチするところまでは同じだが、そこから取り込むx86命令は、Yonahまでが最大3命令/サイクルだったのが、Meromでは6命令/サイクルに増加している。これは後述するMacro Fusionの効果で、ピーク時には5命令/サイクルで命令のデコードができることに対応したものだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ