前回までに、CPUには複数のキャッシュが搭載されていることを説明した。今回はそのキャッシュをどう制御するか、という話をしよう。

3階層のキャッシュのどこにデータを置くか?

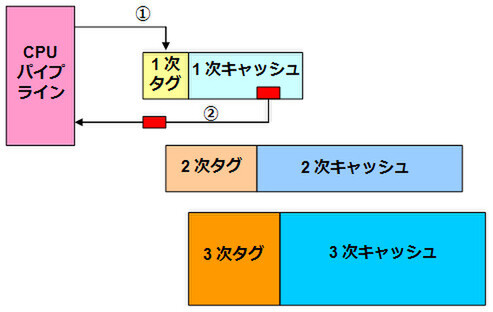

例えば図1のように、1次~3次までキャッシュを持つCPUを考えてみる。ここでCPUがデータ(命令でもいい)のフェッチを掛けた場合、まずは1次キャッシュのタグを検索する(図1-①)。ここで見つかれば問題なく、単に1次キャッシュからそのデータを引っ張ってくる(図1-②)だけでいい。問題は1次キャッシュにデータがなかった場合(キャッシュミス)である。

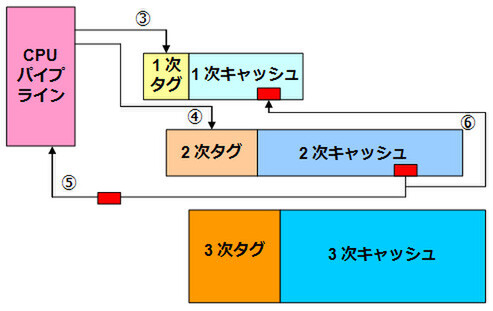

図2は、2次キャッシュでヒットした場合だ。まず1次タグを参照し(図2-③)、ここにないことがわかったら、次は2次タグを参照する(図2-④)。2次タグで発見したら、2次キャッシュからデータをフェッチする(図2-⑤)とともに、1次キャッシュにもキャッシュフィル(データのコピー)を行なう(図2-⑥)。

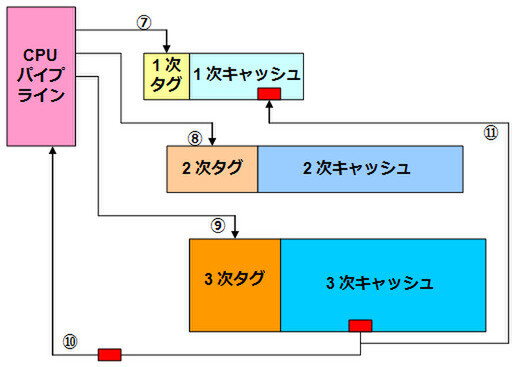

これは1次ミス/2次ミス/3次ヒットの場合でも同じである(図3)。今度はまず1次タグ(図3-⑦)/2次タグ(図3-⑧)/3次タグ(図3-⑨)と順に参照して、3次タグで発見したらそこからフェッチする(図3-⑩)とともに、1次キャッシュへのフィルも行なう(図3-⑪)。

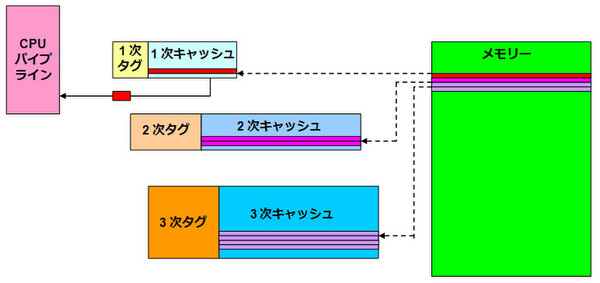

問題は、この1次/2次/3次キャッシュに、何がどのタイミングで入るのか、である。通常のCPUでは、「Implicit Prefetch」(暗黙のプリフェッチ)という機構が利用される。例えば図4のような仕組みだ。

CPUがあるメモリーアドレスのフェッチを要求し、1次/2次/3次とすべてのキャッシュがヒットしなかったケースを考えてみる。この場合、CPUはそのメモリーアドレスを指定してメモリーアクセスするわけだが、通常この際には、1ライン分のメモリーを取得する(取得したと思っている)。しかし、実際には指定したアドレスから7ライン分のメモリーを取得し、1次キャッシュには目的のラインを、2次キャッシュには目的のラインに続く2ライン、3次キャッシュにはさらに続く4ラインを同時に格納するといったメモリーの取り込み方をする。

これにより、例えば1次キャッシュに取り込んだラインを使い切っても、その次の領域は2次キャッシュに、さらにこれに続く領域は3次キャッシュにすでに取り込まれている。だから、最低限のレイテンシーで7ライン分までアクセスできることになる。

ちなみに、これはあくまでも概念であって、実際の実装方法は異なったものである。例えばインテルの場合、「Pentium M」「Pentium 4」までで利用された方法と、Coreマイクロアーキテクチャーで採用された方法では、特に2次/3次キャッシュに対するキャッシュフィルの方法が若干異なる。同じメーカーのCPUでも、アーキテクチャーによってこのあたりの方法論は変わることがある。

この連載の記事

-

第832回

PC

Intel 18AでSRAMは進化したか? Synopsysが挑む最適化技術とWrite Assistの新アプローチ -

第831回

PC

Intel 18AはTSMCに対抗できるか? RibbonFET/PowerVIAの可能性と限界 インテル CPUロードマップ -

第830回

デジタル

HPCからAI向けに用途を変えたInstinct MI350X/400X AMD GPUロードマップ -

第829回

デジタル

2026年にInstinct MI400シリーズを投入し、サーバー向けGPUのシェア拡大を狙うAMD AMD GPUロードマップ -

第828回

PC

TOP500の4位に躍り出たJUPITER Boosterは効率と性能/消費電力比が驚嘆に値する -

第827回

PC

オーディオとモデムを普及させるのに一役買ったAMRとACR 消え去ったI/F史 -

第826回

PC

PCIeリリース直前に登場しわずか1年の短命に終わったCSA 消え去ったI/F史 -

第825回

PC

バッファがあふれると性能が低下する爆弾を抱えるもライセンスが無料で広く普及したAGP 消え去ったI/F史 -

第824回

PC

AT互換機が普及するきっかけとなったPCIは、MCAの失敗から生まれた 消え去ったI/F史 -

第823回

PC

Intel 18AはIntel 3と比較して性能/消費電力比が15%向上 インテル CPUロードマップ -

第822回

PC

爆発的に普及したことが逆に寿命を縮める結果になったVL-Bus 消え去ったI/F史 - この連載の一覧へ