10nmプロセス壊滅の報道に

インテルが敏感に反応

前回お約束したとおり、今回はインテルの10nmプロセスの話をしよう。少し前の話になるが、10月22日にSemiAccurateで“Intel kills off the 10nm process”という記事が出た。

この記事の是非はともかくとして、それが話題になったのはむしろインテルの反応であった。インテルの公式Twitterアカウントの一つであるIntel News(@intelnews)が、この記事が出るや否や直ちに「記事は正しくない。我々の10nmプロセスは順調であり、歩留まりは前回の投資家向けレポートで説明したように改善している」と反論を公開。

Media reports published today that Intel is ending work on the 10nm process are untrue. We are making good progress on 10nm. Yields are improving consistent with the timeline we shared during our last earnings report.

— Intel News (@intelnews) 2018年10月22日

多くのメディアが内容そのものよりも、インテルがかくも敏感にこれに反応したことをレポートする(例えばTOP500のニュース)といった珍事があった。

前回も説明した通り、インテルにとって10nmプロセスは、いまや同社の将来がかかっていると言っても過言ではないほど重要な要素になっている。

仮に10nmプロセスが全部撤回になったらどうなるかというと、2021年以降急速にシェアを落としていくのが目に見えており、しかも10nm関連に向けての過去の累積投資(特にD1B/D1C/D1D/Fab 28/Fab 32の各Fabに納入した10nm向けの製造装置を含む設備)を最悪全部損金扱いで償却する必要がある。これは同社の財務状況に強烈なインパクトがあるだろう。

優良企業のインテルが一発で赤字企業に転落しかねないほどにまで10nmに資金を突っ込んできたわけで、その意味でも10nmを止めるというニュースが広く伝わることは絶対に避けねばならない、というのは実にわかりやすい。

ただこのあまりに早いレスポンスは、むしろ「そんなに順調なら、なんでまだ出荷されないの?」という素直な疑問につながってしまうのは当然である。(先のインテルのツイートに対するメンションもおおむねそのようなコメントである)。

では実際は? というと前回書いた通り、現在インテルの10nmに関しては本気で箝口令が敷かれており、まったく情報が伝わって来ない。したがって、以下は周辺情報を元にした筆者の推測である。

配線層だけでなく

プロセス自体を作り直し

まずインテルは今なにをやっているかというと、おそらくは10nmプロセスの作り直しと、10nmプロセスを利用したチップ(要するにIce Lake)の作り直しをしているのだと思われる。

元々、チップの配線層の作り直しをしているという話は伝わってきていたが、その時点で既存の配線層の構造のままで作り直しても改善は難しいだろう、という気はしていた。そこに来てこのインテルの反応だけに、おそらくはプロセスの作り直しも含んでいるのだろう、と筆者は確信している。

まずは配線層の作り直しについてだ。以下のスライドは2017年のIntel Technology & Manufactureing Dayで示されたものである。

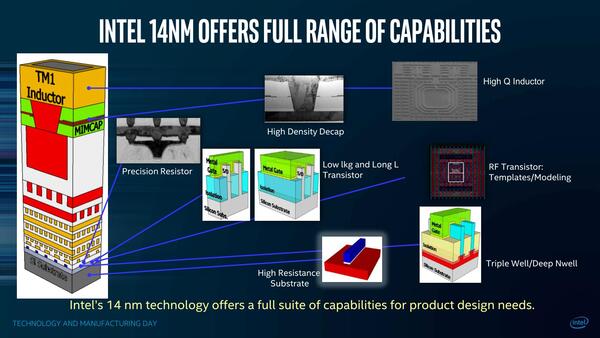

まずは基礎のおさらいを。左がチップの一部を切り出した部分である。一番下のグレーの部分がシリコン基板、その上のやや青味がかった部分がFinFETトランジスタを構築している部分である。その上の黄色い部分や赤い部分が配線層となる。

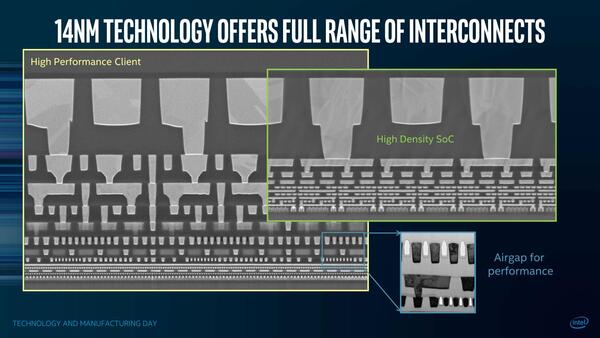

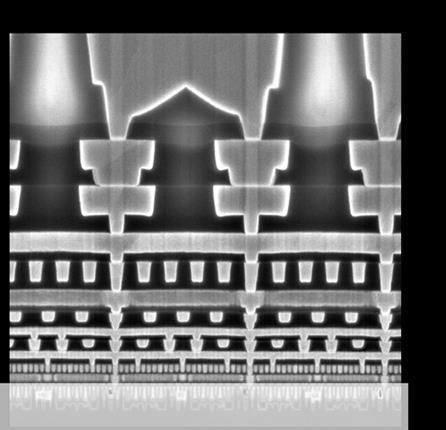

ちなみにこれは14nmプロセスのものであるが、細かい部分はともかくとして基本的には10nmも同じである。その配線層をさらにアップにしたのが下の画像だ。一番下がトランジスタで、その上に配線層が延々と重なる格好になる。

ちなみに2017年にインテルが公表した、10nm世代の配線層は以下の通り。この配線層、下からM0(Metal 0)、M1、...と来てM10まであり、その上にTM0/TM1(コンタクト)が重なる。コンタクトはパッケージと接続される部分で、このため傍目にもM0~M10と明らかに大きさが違う。

IEDMでインテルはこのM0~M10とTM0/TM1の配線間隔と素材を公開しており、以下のようになっている。

| インテル10nm世代の配線間隔と素材 | ||||||

|---|---|---|---|---|---|---|

| 配線層 | 配線間隔 | 配線素材 | ||||

| M0 | 40nm | コバルト | ||||

| M1 | 36nm | コバルト | ||||

| M2~M4 | 44nm | 銅 | ||||

| M5 | 52nm | 銅 | ||||

| M6 | 84nm | 銅 | ||||

| M7/M8 | 112nm | 銅 | ||||

| M9/M10 | 160nm | 銅 | ||||

| TM0 | 1.08μm | 銅 | ||||

| TM1 | 11μm | 銅 | ||||

M0とM1は後述するSAQPという技法で構築されており、しかも配線材料がコバルトになっている。これは連載464回で書いたようにエレクトロマイグレーション対策である。ところが、そうでなくても配線が細くなっているところに、銅に代えて抵抗値の高いコバルトを使った結果として配線遅延がシャレにならなくなってしまった。そこで配線をやり直そうという話になったわけだ。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ