Bristol RidgeとCarrizzoの違いは

可変電圧、信頼性、電源管理

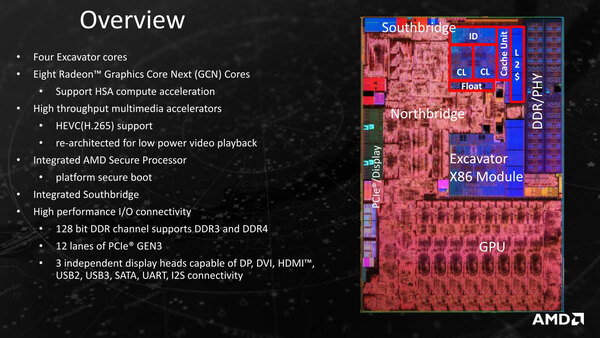

そのBristol Ridgeであるが、Carrizzoから細かな変更がいくつかなされている。これをかいつまんで説明したい。Bristol RidgeはCarrizoコアにDDR4のサポートを追加したもので、ベースになるのはMerlin Falconである。

連載338回で触れたとおり、Merlin Falconは単にCPU/GPUのみならずチップセット機能まで統合したSoCであるが、Bristol Ridge(やこの後出てくるSummit Ridge)も同様にチップセット機能をある程度CPU側に持つことになるようだ。

周辺機能が違うだけではなく、コアそのものにもずいぶん手が入った。それはプロセッサーのパイプライン構造そのものではなく、むしろ物理設計に関わる部分である。

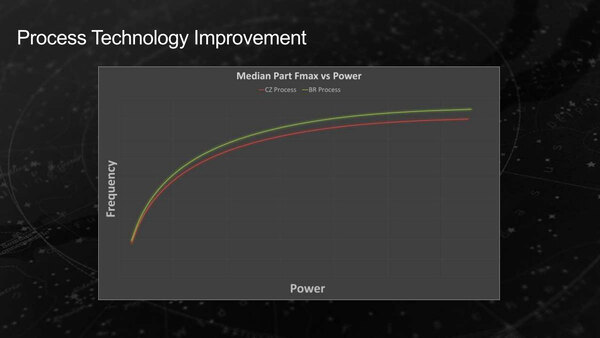

まずBristol Ridgeは、Carrizoと比較した場合に、同じ消費電力であれば若干ながら高い動作周波数を実現できるようになった。これを実現する1つ目は、より高精度なAVFSの動作である。

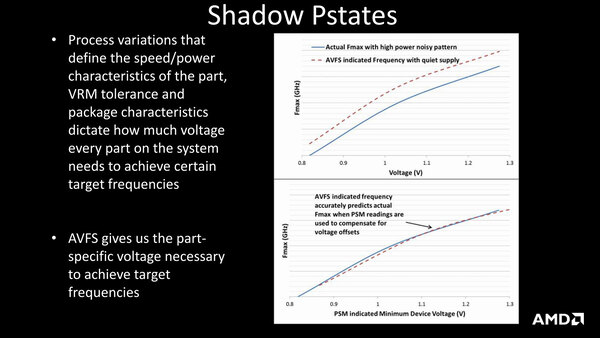

一般にFVSは、「あらかじめ」動作周波数にあわせた電圧のテーブルを持っており、あとは動作周波数の変化に合わせて電圧を変化させる。もう少し厳密に説明すれば、以下のステップとなる。

- (1) 「動作周波数を引き上げよう」と内部のロジックが判断する

- (2) ターゲットとなる動作周波数に必要な電圧を内部のテーブルから引っ張り出す

- (3) 外部のPMICに対してその電圧に変化させるように指示を出す

- (4) 電圧が変化するまで一定時間待つ(この時間は仕様で決まっている)

- (5) 動作周波数の引き上げを行なう(ベースクロックに対する倍率を変化させる)

問題になるのは(2)である。というのは、内部のテーブルはチップ単位で個別に設定したものではなく、いわばチップの代表値をベースに構築されているからだ。半導体は当然特性にブレがあり、この結果としてテーブルの値と実際の値には若干の差があることは珍しくない。(前述のAVFSの表上段参照)

Bristol Ridgeではこれをなるべく現実のチップに近いものに追い込むこと(AVFSの表下段参照)で、無駄な電力の消費を抑えるようにした。ポイントは、これがAdaptive(適用型)、つまり実際の状況を見ながら調整するという点だ。

詳細は未公開であるが、一般にはダイ上の何箇所かに、電圧/周波数のマッチングを評価するための回路を用意しておき、ここで電圧/周波数の特性を測定しながら最適な電圧になるように調整する、というメカニズムは昔から提案されてきており、これに類した回路を搭載しているのではないかと思われる。これにより、製造時のバラつきがあっても最適な電力で動作することになる。

この例の場合、電圧にあわせて動作周波数を低めに抑えることで乖離を減らすようにする形になると思われる。性能そのものは若干落ちるが、動作周波数/消費電力比は改善することになる。これを暗黙のうちに行なう、ということでShadow Pstateという表現がなされている。

ちなみに前述のAVFSの画像は想定よりも悪いチップでの例であるが、逆に想定よりも良いチップであれば同じ周波数でより電圧を下げられるわけで、ここで多少なりとも性能/消費電力比を改善できることになる。

次が信頼性トラッキングである。半導体も工業製品であるから、当然いつかは壊れる。なぜ壊れるのか、なぜ劣化するのかという話は要因がたくさんあり、しかもまだ理由が解明できていないものもあるのだが、経験則的に「このくらいの寿命を持たすにはこのくらいの構造にすれば良い」というのはある程度見えており、これにあわせた形で半導体メーカーは製品を製造している。

経年変化は通常トレースしていないわけだが、Turbo Coreのようなオーバークロック動作の場合には通常よりもストレスがかかるため、劣化が加速する傾向にある。

そこで、実際の劣化の累積具合をキチンとトレースして管理することで、寿命一杯まで使いきろう、というのがこちらの趣旨である。

オーバークロック動作を煩雑に行なうと、一時的に不具合の累積が想定するゴールを超えることは当然ありえる。これは想定寿命より早くチップが劣化するという意味で、動作はするが消費電力が増えたり、動作周波数があがりにくい状況になる。これを想定カーブ内に抑えることで、設計寿命一杯までフルに使えるようにしよう、というものだ。

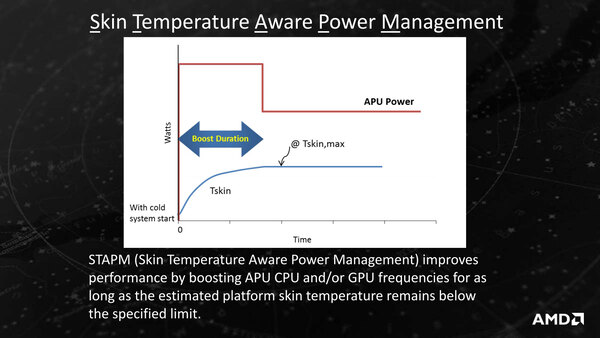

3つ目はデスクトップ向けにはあまり関係ないが、ノートなどに関係する話で、皮膚温度配慮の電源管理(STAPM)を搭載したことだ。

特にノートやタブレットなどでは、温度が上がりすぎて持てないことにならないように、機器の外部温度(Tskin)を一定内におさえる必要がある。STAPMはTskinを見ながらBoostの管理を行うようにするためのメカニズムである。

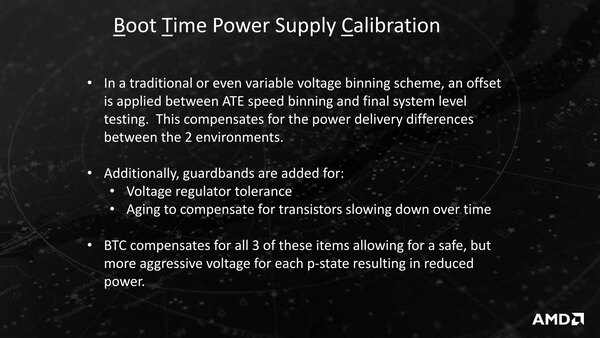

最後がBTC(Boot Time power supply Calibration)である。これは先のAVFSの話とも近い話であるが、チップには当然製造時のバラつきがあるのと同様、マザーボード側の電源供給回路の側も当然バラつきがある。このバラつきを最小限に抑えることで、より効率を改善させようというものだ。

ちなみにスライドではチップについても、元々後工程の工場におけるチップ単体での評価性能と、最終的にパッケージされ、システムに搭った状態での評価性能の間にも若干のずれがあることにも言及している。

これも工業製品である以上当然だが、やはり誤差というものはなにを作る場合でも存在しており、設計はその誤差を見込んだ形で行なうのが一般的である。ただそれは最適化された、という状態ではないので、もう一段追い込んでやろう、という話である。

具体的には電源投入時にいきなり起動するのではなく、まず複数の電圧の設定指示を電源回路に出し、チップ内部の電圧センサーを利用して「電源供給回路に指示した電圧と実際に供給された電圧」の差を確認、さらに温度を測定することでシステムの特性を確認。以後はそのシステムの特性に合わせる形で電圧指示を電源供給回路に出すことで、精度を引き上げようというものだ。

通常はここまで凝ったことはしない。それよりプロセス微細化を進めたほうが効果が高い、というのが一般的であるが、Bristol Ridgeでは28nmを引き続き使っている関係なのか、コアそのもののアーキテクチャーは変えないまま省電力化を進めた。これは先のBristol Ridgeの概要を示した画像でも“Four Excavator cores”と明記されている。

ただこの技法は別に28nmだけで有効というわけではないので、今後出てくるSummit Ridgeにも同様のメカニズムが搭載されることになるであろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ