47万5000ドルと安価な

Convex C2シリーズ

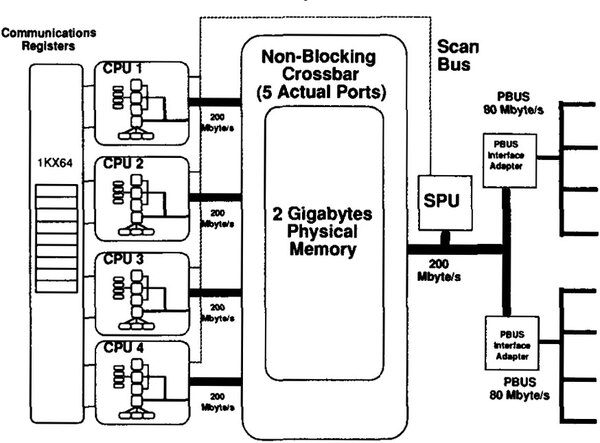

さて、このC1をもう少し高速化したのが次のC2である。当初はCXS(Convex Extended SuperComputer Architecture)という呼び方がなされ、製品名もC1 XLだったが、どこかのタイミングでわかりやすいC2に切り替わったようだ。

このC2ではいくつかの改良がなされている。まずは4コアの密結合プロセッサー構成としたことだ。

このあたりはCRAY X-MPと似ているが、通信レジスターを1024個用意したり、メモリー間帯域を200MB/秒まで広げるなど、性能を落とさない工夫をしている。

※画像の出典は、"THE CONVEX C240 ARCHITECTURE"。

加えてプロセッサーそのものの高速化も行なわれた。C1とC2は基本的なアーキテクチャーには一切変更がない。物理メモリーを2GBまでサポートする程度であるが、製造技術はCMOSとECLのハイブリッドとなっている。

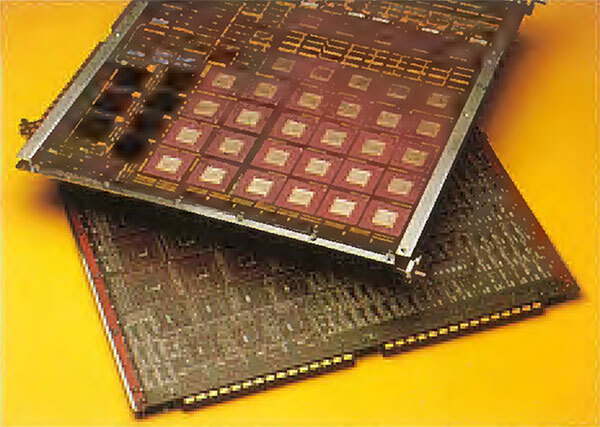

論文によれば、スカラーユニットは合計100KゲートのECLで製造されたが、これは富士通が提供する3000/4500/10000ゲートのECLゲートアレイで構成された。

またベクトルユニットは、20000ゲートのCMOSゲートアレイと4000/4500ゲートのECLゲートアレイのハイブリッドだ。

システム全体としての動作周波数は25MHzであるが、主要な回路部分は50MHz動作となっている。下の画像が当時のプロセッサーボードであるが、ECLのゲートアレイが整然と並んでいるのがわかる。

※画像の出典は、同社の1998年のカタログ“The CONVEX C Series”。

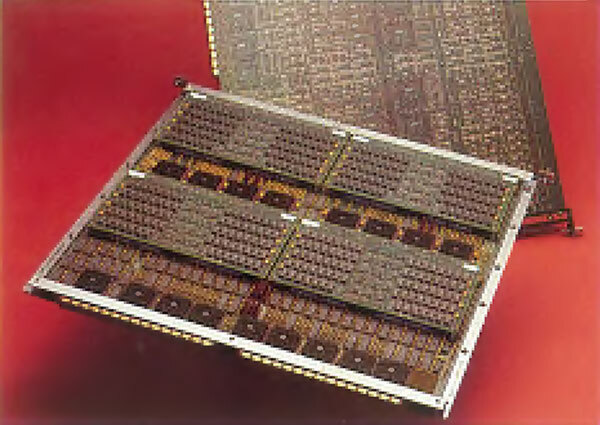

一方下の画像がメモリー用のクロスバースイッチ(とおそらくはメモリーモジュール)で、こちらはECLベースだそうだ。

※画像の出典は、同社の1998年のカタログ“The CONVEX C Series”。

C2シリーズは1998年にリリースされるが、さまざまな構成と動作周波数をサポートした。カタログによればC2世代では以下の6モデルがラインナップされている。

| C2世代のラインナップ | ||||||

|---|---|---|---|---|---|---|

| モデル名 | CPU数 | 動作周波数 | 性能 | |||

| C201 | 1 | 18MHz | 36MFLOPS | |||

| C202 | 2 | 18MHz | 72MFLOPS | |||

| C210 | 1 | 25MHz | 50MFLOPS | |||

| C220 | 2 | 25MHz | 100MFLOPS | |||

| C230 | 3 | 25MHz | 150MFLOPS | |||

| C240 | 4 | 25MHz | 200MFLOPS | |||

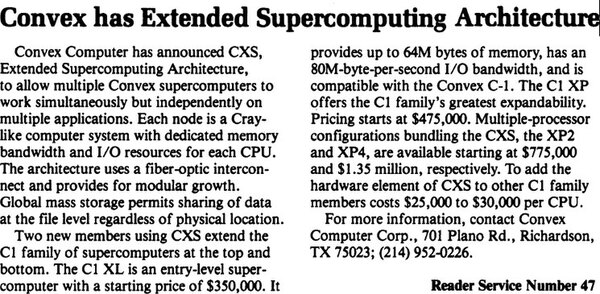

ちなみにこのConvex C2シリーズはお安かった。下の画像はCOMPUTERWORLDの1986年12月号に掲載された新製品紹介の抜粋だが、この当時の予想価格ではプロセッサー1つのもので47万5000ドル、4プロセッサーの最上位構成での135万ドル程度を想定していた。

あるいは実際の価格を調べてみると、computermuseumのページによれば、ロンドン大学バークベック校が1992年にC220を導入したときの価格がおよそ140万ドルだったそうである。

冒頭に紹介した、SCDに納入されたCRAY X-MP/48と単純に比較は難しいが、仮にC240の価格がC220の倍だとすると280万ドルほどなので、Convex C240の価格はおおむね5分の1となる。

一方性能はCRAY X-MPのプロセッサー1台の理論性能が210MFLOPSほどなので、Convexの方は4分の1となる。

つまり価格/性能比で言えばConvexの方が20%ほどCRAYを上回っている。このあたりは同社の目的がきちんと達成された形になる。

→次のページヘ続く (ガリウム砒素を採用したConvex C3)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ