今回はCPU黒歴史をお休みして、インテル「Xeon」のロードマップをアップデートしたい。基本的には連載89回と差がないのだが、妙なものが投入されることがわかったのでご紹介しよう。

CPU同士の接続用に位置づけが変わった

Sandy Bridge-EN/EPのQPI

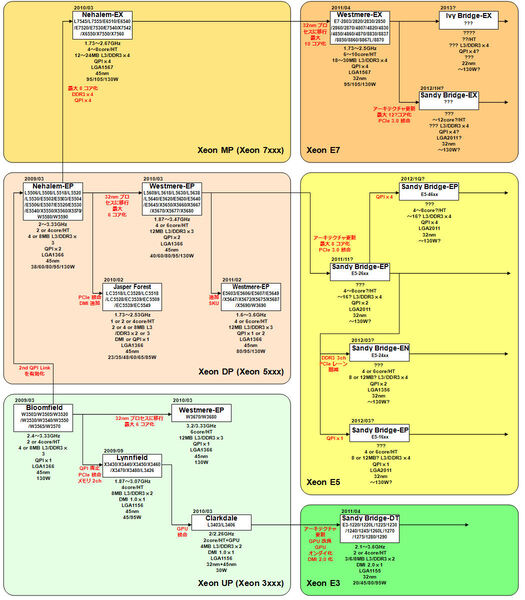

まず89回とのロードマップ図の違いを見ると、「Westmere-EX」ベースの製品に「Xeon E7-8870」が、「SandyBridge-DT」ベースの製品に「Xeon E3-1290」が追加された程度である。

また89回のロードマップ図では、「Xeon E5-24xx」と「Xeon E5-16xx」の投入時期が「2010/03?」となっていたが、これは「2012/03?」の誤りだったので、これを修正している。「SandyBridge-EP」ベースの「Xeon E5-26xx」は、89回は「2011年10月?」と記したが、11月になりそうな雰囲気だ。

基本となる製品動向に変化はないが、通信機器向けを中心に変則的な製品が投入されることがわかった。89回も解説したとおり、AMDの「4プロセッサー Tax」対抗のためにインテルは「Xeon E5」のパッケージを、当初予定していたLGA1356からLGA2011に切り替えた。

ただし、全製品を切り替えたわけではなく、「Xeon E5-24xx/26xx/46xx」がLGA2011、「Xeon E5-16xx」がLGA1356という妙な構造になっている。ここで重要なのは、LGA1356が生き残ってしまったことであるが、これが妙な構成で利用されるということだ。

図1は「Sandy Bridge-EN」を使った場合の2プロセッサーシステムの構成図である。QPIは1レーンのみ(速度は8.0GT/秒)で、チップセットの「Patsburg SSB-D」との接続は(LGA1366時代の)QPIに代えて、「DMI 2.0+PCI Express Gen3 x4」という構成になっている。

Sandy Bridge-ENはGPUを省いた代わりに、PCI Express Gen3を最大36レーン搭載する。そのためチップセットの接続も、PCI Expressのみでいいと判断したようだ。そのためQPIは、純粋にCPU同士の通信だけに使われるインターフェースに切り替わった。

これが「Sandy Bridge-EPに切り替わるとどうなるか?」というのが図2である。本来Sandy Bridge-EPでは4プロセッサー以上の構成を可能にするシステムだったので、QPIのレーン数が多い。そのため2プロセッサー構成では、2本のQPIレーンを使ってCPU同士を接続するという構成になっている。DDR3は4チャンネルとなり、またPCI Express Gen3は合計40レーンに増えている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ