Intelチップセットの歴史 その5

DDR3に先鞭をつけたIntel 3~4世代のチップセット

2009年12月14日 12時00分更新

結果として先送りされたDMIの高速化

Nehalem世代にも尾を引く

Intel 4シリーズはDMIを高速化する絶好のチャンスだった。前回も触れたとおり、DMIはPCI Expressをベースとしている。従って(G)MCHとICHの両方にPCI ExpressのPHYが搭載されているわけだ。そしてIntel 4シリーズでPCI Express Gen2が搭載されたので、(G)MCH側のDMIのPHYも、当然Gen2対応になっていると考えられる。わざわざGen1とGen2、両方のPHYを搭載するメリットはないからだ。Gen2はGen1との互換性を保つのを必須条件としており、サイズ的にもほとんど差がない。あえてGen1を残すとしたら、余程Gen2のPHYが不安定だとか、動作検証のコストが出なかったとか、その位しか理由はない。

ただ(G)MCHはともかく、ICHの方は当分Gen2対応にはできない。というのも、ICH10はいまだに130nmで製造されており、90nmならばともかく130nmのチップで、5GT/秒の転送速度の実現はかなり厳しいからだ。結果として、DMIは引き続き2.5GT/秒のx4レーンが維持されてしまった。これが引き続きNehalem世代まで使われるようになったのは、インテルとしてはやや残念なところだろう。

今回のまとめ

・2007年6月に登場した「Intel 3」シリーズから、インテルはDDR3 SDRAMへの対応を始めた。ただし、当時は価格や性能面でのメリットは希薄だった。

・Intel 3シリーズもバリエーションは豊富に登場した。ハイエンド向けに「Intel X38/X48」が登場したほか、GPUをやや強化した「Intel G35/G33/G31」、ビジネス系プラットフォームの「Intel Q35/Q33」などがラインナップされた。

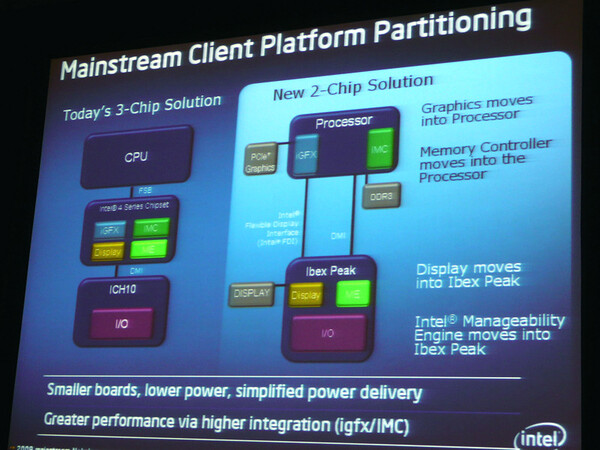

・2008年6月には、現在の主流である「Intel 4」シリーズが登場した。(G)MCHがPCI Express Gen2に対応した点が大きな変更点。メモリーは変わらずDDR2/DDR3の両対応のままで、DMIの高速化も行なわれなかった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ