今週は業界に痕跡を残して消えたメーカーをお休みして、久々にスーパーコンピューターの話である。11月12日~17日にコロラド州デンバーでSC17(Supercomputing Conference)が開催された。

TOP500のランキングもこれに合わせて更新され、日本の海洋研究開発機構(JAMSTEC)が導入した暁光(Gyoukou)が絶対性能で4位(19.1PFLOPS)になり、一方性能効率を競うGreen 500では1~3位+5位が全部PEZY-SC2で占められる(遂にトップは17GFlops/Wを超えた)という結果になるなど、いろいろと変化があったのだが、その話はおいておく。

画像の出典は、“JAMSTECのプレスリリース”

コードネーム“Knights Hill”こと

第3世代Xeon Phiが開発中止

このSC17の開催に合わせ、インテルのTrish Damkroger氏(VP, Data Center Group and GM of Technical Computing Initiative)は“Unleashing High-Performance Computing Today and Tomorrow”と題するブログ記事を掲載したが、この中でさらっとKnights Hillの開発を中止することを発表した。

当該部分を抜き出すと“One step we're taking is to replace one of the future Intel Xeon Phi processors (code name Knights Hill) with a new platform and new microarchitecture specifically designed for exascale.”(我々はExascaleに向けた新しいマイクロアーキテクチャとプラットフォームの製品を、Knights Hillで知られていた将来のXeon Phiと入れ替えることを決めた)とされている。

ちなみにこの決定は、顧客の要望によるものである、というのがDamkroger氏の説明である。この説明をもう少し細かく紹介したい。まずは「顧客の要望」である。

もともと1995年あたりから、米国のスーパーコンピューター戦略を牽引してきたのがASCI(Accelerated Strategic Computing Initiative)/ASC(Advanced Simulation and Computing program)だという話は連載286回で説明した。

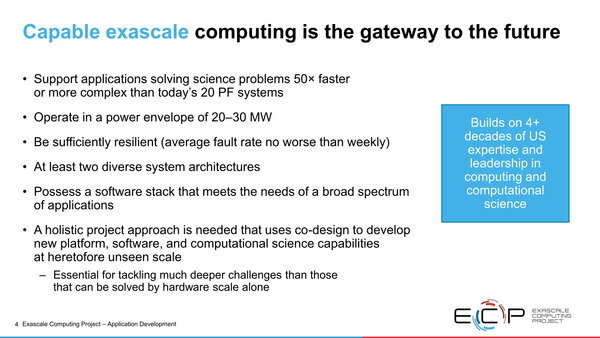

このプログラムは現在も継続中で、ローレンス・リバモア、ロスアラモス、サンディアの国立研究所に分散する形で開発や利用が続けられているわけだが、これとは別に(厳密には全然別ではないのだが)ECP(Exascale Computing Project)と呼ばれるプロジェクトが2016年あたりから動き出している。

ECPの前身は2015年にオバマ前米大統領の下で立ち上がったNational Strategic Computing Initiativeであり、そのさらに前身は2008年に米エネルギー省内の科学部と国家核安全保障局が共同で始めたプロジェクトに遡る。

このプロジェクトには、その後サンディア国立研究所とオークリッジ国立研究所も加わり、2013年にはDOE Exascale Initiativeとして基本的な要求がまとめられた。ここで示されたのが「2020年(後に2022年に訂正)に、ピーク性能1 ExaFlopsのマシンを20MW以内の消費電力で実現する」という、基本方針である。

さてこのDOE Exascale Initiativeを下敷にしてNational Strategic Computing Initiativeが示され、これを元に実際にExascaleのマシンを構築しよう、というのがECPという組織である。

ちなみにECPの資料を読んでいると、性能そのものは1EFLOPS(現在ある20PFLOPSマシンの50倍)で変らないが、運用時の消費電力は20~30MWになっており、やはり20MWの枠は厳しいようだ。

画像の出典は、2016年9月のASCAC(Advanced Scientific Computing Advisory Committee Meeting)における、オークリッジ国立研究所Douglas B. Kothe氏の資料“Exascale Applications: Opportunities and Challenges”

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ