動作周波数あたりの性能が高い

PA-RISCをプロセッサーに採用

このPA-RISCについては、以前Mercedの回で少し触れただけなので、細かく説明しよう。

PA-RISCのご先祖様は、HPが1982年に発表したHP 9000/500シリーズというワークステーションに利用されていたFOCUSと呼ばれるプロセッサーである。このFOCUSそのものは純粋にCISCで、Bit Slice方式のStackアーキテクチャーを利用したものである。

1.5μmプロセスのNMOSで製造され、トランジスタ数は45万、動作周波数は18MHzだったと伝えられている。このFOCUSの性能を上げるべくいろいろ開発していくなかで、RISCを利用して性能を上げよう、という試みが最終的にPA-RISCとなって結実した。ちなみにPAはPrecision Architectureの略である。

最初に定義されたPA-RISC 1.0は1986年に発表された。これに基づくCPUとしては、TS-1/NS-1/NS-2/PCXの4種類がある。TS-1はある意味本当の試作品のようなもので、8MHz動作、1次キャッシュは128KBという構成で、シングルパイプラインの構成である。

これをもう少し実用的にすべく作られたのが、動作周波数を30MHzまで上げたNS-1(1987年)と、動作周波数は27.5MHzどまりながら1次キャッシュを1MBに増量し、さらにマルチプロセッサー構成を可能にしたNS-2(1989年)が登場する。

最終的に1990年にリリースされたPCXは、NS-2に似た構成ながら50MHzまで動作周波数を引き上げる。

ただこのPA-RISC 1.0に基づくCPUはいろいろ制約が多かった。PA-RISCの命令フォーマットは昔のRISCらしく、主要な命令は1サイクルで実行可能で、マイクロコードは利用せず、命令長は32bit固定。メモリーアクセスはLoad/Store命令のみ、といった具合である。

レジスターは汎用が32個、シャドウレジスターが7個あり、論理アドレスは48bitとなっている。このあたりは使いやすそうな感じであるが、その一方でメモリー管理ユニットも仮想記憶のサポートもないというのは、本格的なOSを載せるのが極めて困難だった。

またプロセスの微細化が遅れたこともあり、1次キャッシュやFPUは全部外付けとされている。というわけで、ここまではある意味試作が続いたようなものである。

このあたりを対策したのが1991年に発表されたPA-RISC 1.1である。大きな違いはメモリー管理ユニットと仮想記憶のサポートだが、この世代からスーパースカラーも実装される。

1991年に発表されたPA-7000は最初にスーパースカラーに対応した製品で、これはまだパイプラインが1本(動作周波数は66MHz)だが、1992年に登場したPA-7100LC/PA-7150はついに2wayのスーパースカラーが搭載された。といっても、最初はALUとFPUがそれぞれ1本づつの構成であるが。そして、動作周波数も100/125MHzに引き上げられた。

ちなみにここまでのプロセッサーはいずれも、昔のPentium IIや初代Athlonのようにプロセッサーモジュール上にキャッシュ用SRAMが外付けされている構成である。

これに続き1994年に登場されたPA-7100LCは低コスト向けということで外付けキャッシュを廃し、その代わりに内部に1KBの1次キャッシュを搭載している(ただし、オプションで外付けキャッシュを利用可能で、これは2次キャッシュ扱いとなる)。

さらにMAX-1と呼ばれるSIMD拡張命令も追加される。このMAX-1は構成も狙いもx86で言うところのMMXと良く似ており、外部アクセラレーターなしでMPE-1のデコードを可能にするというものだった。

ただし、MAX-1は1 CPUのワークステーション向けの製品ということで、SMPのサポートは削られているため、SPP 1000は向かないものだった。もっとも開発時期を考えると、1994年登場のPA-7100LCではSPP 1000のリリースには間に合わないのだが。

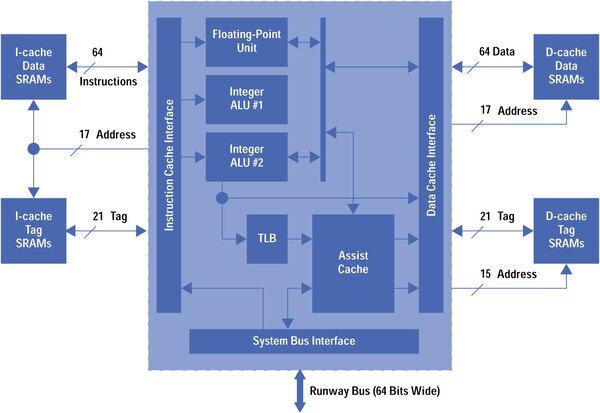

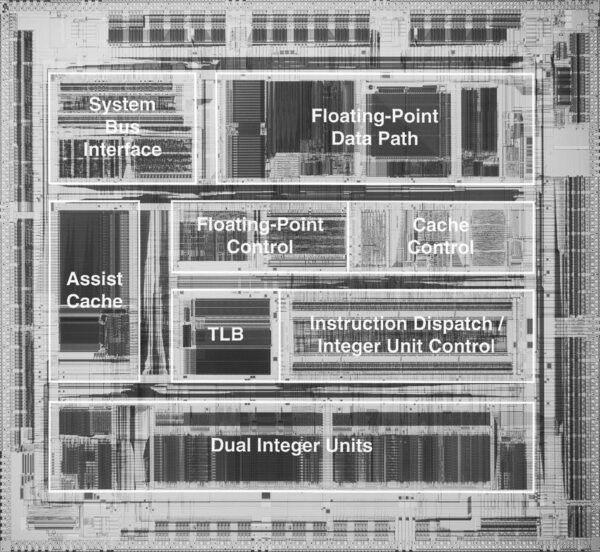

さて、これに続いて1995年に登場したのがPA-7200である。こちらは下の画像のように、2本のALUと1本のFPUを持つスーパースカラー構成の製品である。

画像の出典は“Design of the HP PA 7200 CPU(Hewlett-Packard Journal February 1996)”

メインとなるキャッシュは相変わらずオフチップ(2次キャッシュ扱い)だが、2KBのアシストキャッシュ(1次キャッシュ扱い)が内蔵されている。

製造プロセスは0.55μmのCMOSプロセスで、およそ126万トランジスタ、動作周波数は最大140MHzだった。このPA-7200の性能を当時の他の製品と比較したのが下の表だ。

画像の出典は、旧MicroDesignのMicroProcessro Report Vol.8. No.3(March 7, 1994)”

| PA-7200の性能比較 | ||||||

|---|---|---|---|---|---|---|

| SPECint92 | SPECfp92 | |||||

| PA-7200 100MHz | 141.0 | 223.9 | ||||

| Alpha 21064 200MHz | 138.4 | 187.6 | ||||

| Pentium Pro 200MHz | 366.0 | 283.2 | ||||

ただAlphaはもうこの時期には21164のリリースを予定していたため、ここで大きく性能を引き上げられる予定であった。それでも140MHz動作にすれば、Alphaには拮抗できそうでも、Pentium Proにはまだおよばない感じで、性能不足は明白であった。

HPはこの後7200のローコスト版として、SMPのサポートを削り、MAX-1を搭載したり(PA-7200にはMAX-1は未搭載)、オンチップキャッシュを128KBまで引き上げたPA-7300LC(最大180MHz)を1996年にリリースした後で、PA-RISC 2.0を発表する。

PA-RISC 2.0では64bitアドレスがサポートされたほか、ついにアウト・オブ・オーダーの実装を可能にするIRB(Instruction Reorder Buffer)の仕様が追加された。

またMAX-1はワークステーション用という扱いで、SMPに対応したCPUには未搭載だったが、PA-RISC 2.0ではこれを拡張したMAX-2が標準で入るようになる。これに基づく最初の製品が、やはり1996年に登場したPA-8000である。

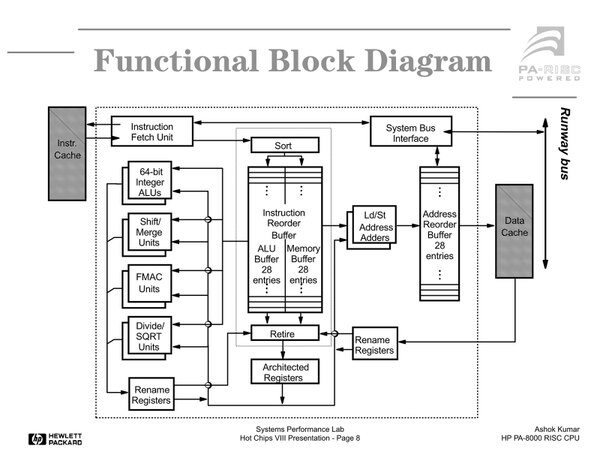

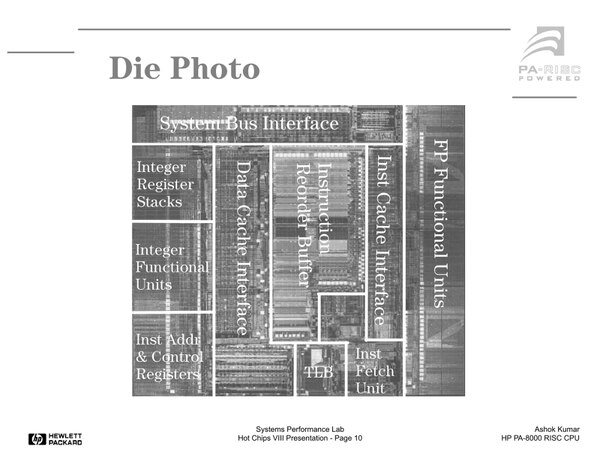

PA-8000は整数演算×4・浮動小数点演算×4・Load/Store×2という10個のパイプラインを持つ4way スーパースカラー/アウト・オブ・オーダーの重厚な構成になった。

画像の出典は、HotChips VIII(1996年)で同社のAshok Kumarが発表した“The HP PA-8000 RISC CPU”

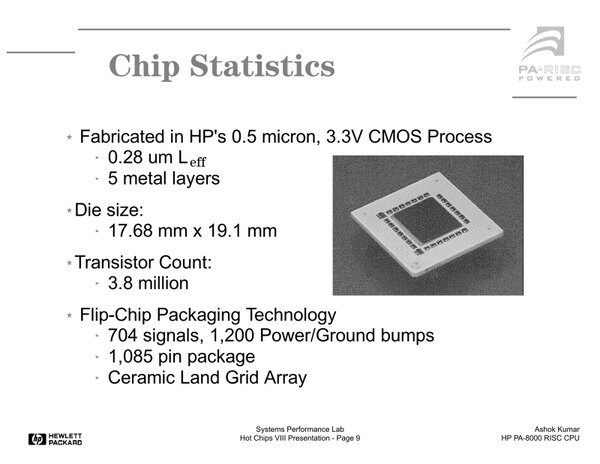

プロセスは同社のCMOS-14C(0.5μm CMOS)を利用し、動作周波数は最大180MHzとされた。

画像の出典は、HotChips VIII(1996年)で同社のAshok Kumarが発表した“The HP PA-8000 RISC CPU”

この連載の記事

-

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 -

第847回

PC

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手 -

第846回

PC

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ - この連載の一覧へ