CPU黒歴史AMD編の第3弾は、「SledgeHammer/ClawHammer」のコード名でおなじみの、第1世代の「K8」アーキテクチャーの話である。K8世代はおおむね成功を収めたと言え、そのおかげか今では忘れられているのだが、出だしの第1世代は散々だった。

99年に発表されるはずが

2002年までずれこんだHammer

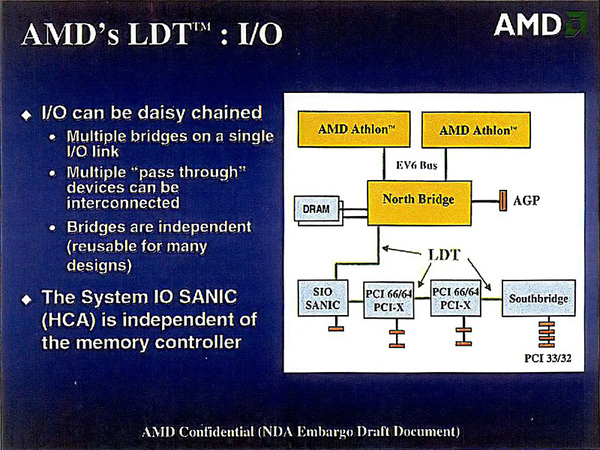

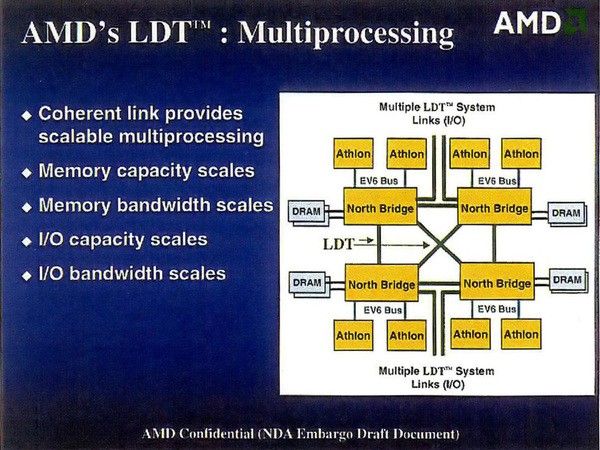

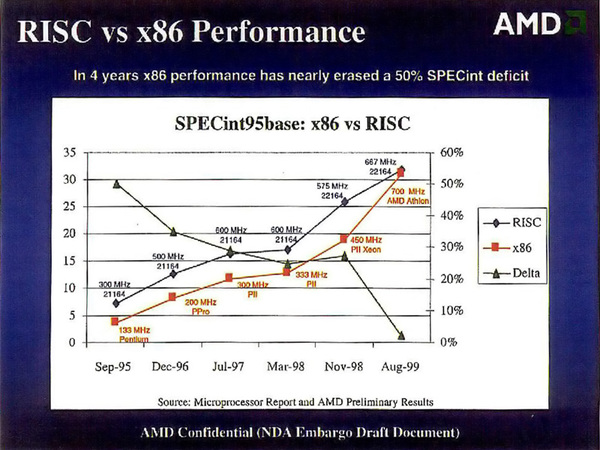

K8ことHammerの構想が最初に発表されたのは、1999年に開かれた半導体業界のイベント「Micro Processor Forum」(MPF)でのこと。講演を担当したのは当時のAMD CTOであるフレッド・ウェバー(Fred Weber)氏である。この時は講演のタイトルは、当初「An Athlon-Family Processor for Workstations and Servers」だったのが、「The AMD Athlon Processor: Future Directions」に変更され、内容もHammerそのものではなく、「LDT」(Lightning Data Transfer)こと「HyperTransport Link」とx86-64命令の説明に終始した(関連記事)。

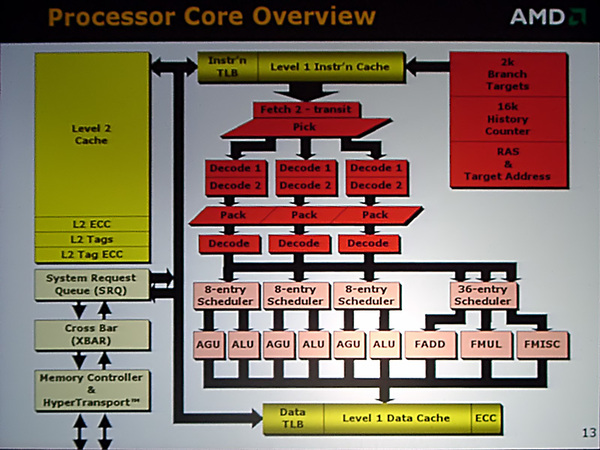

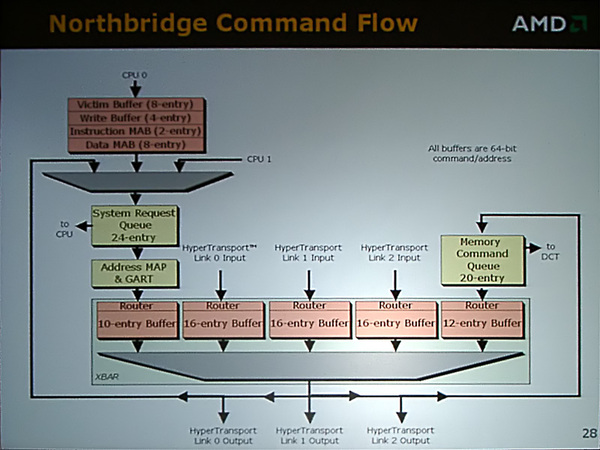

翌2000年のMPFでは、「Athlon MP」とAMD-762チップセットが申し訳程度に紹介されただけで、この時点ではx86-64の話なども一切なし。しかし、2001年のMPFでは再びウェバー氏が登壇し、ここで初めてHammerアーキテクチャーが発表された。

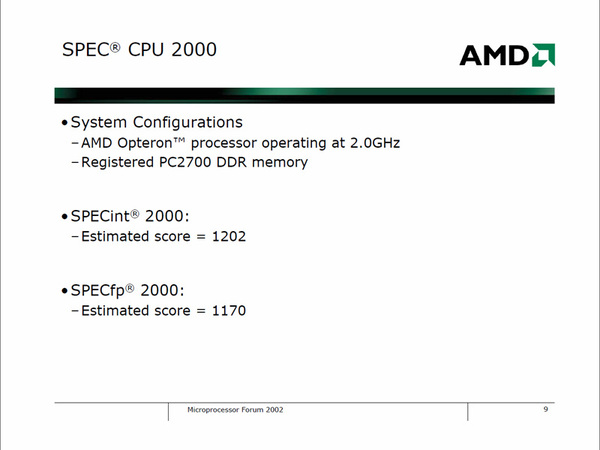

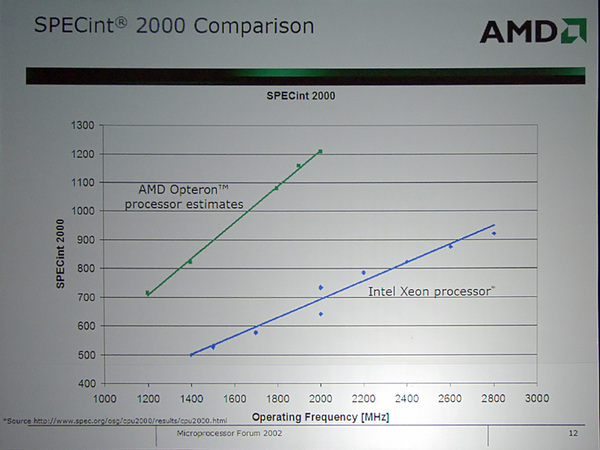

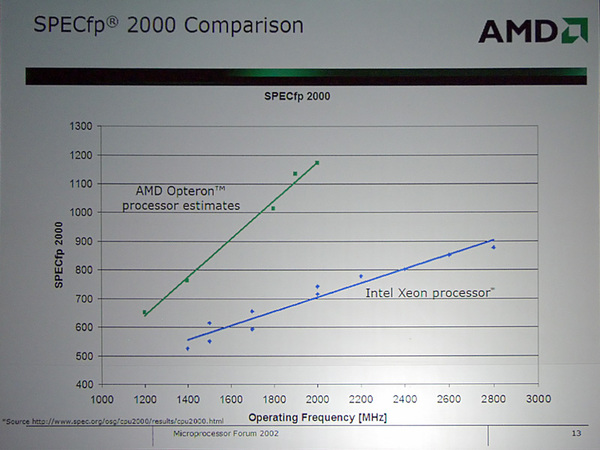

発表時点では性能に関する話は皆無であった。性能についての説明があったのは、翌2002年のMPFである。当時のスライドではSPECint 2000とSPECfp 2000の数字のみが示されているが、講演会場では動作周波数に応じての性能も示されていた。また、マルチコアにおけるメモリー帯域も公開され、拡張性が確保されていることが示された。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ