GDDR3

GDDR2の延長にあるのがGDDR3である。GDDR2との違いとしては、「DQS」(Data Strobe信号)が「RDS」(Read Data Strobe信号)と「WDQS」(Write Data Strobe信号)に分割され、読み書きのタイミングを別々に取れるようになったこと。そして、ハードウェアリセット機能が搭載されたという、2点の違いがある。製造プロセスは70nm辺りを使うことが多く、そのためGDDR2よりも動作電圧が下げられている。

GDDR3の標準化は2003年9月と、GDDR2とほとんど間がない。また信号線などもほぼ同じ(DQSとリセットのみ配慮すればいい)とあって、GDDR3対応のGPUは、実際にはGDDR2とGDDR3の両対応になっていることが一般的だ。一応ローエンドがGDDR2で、メインストリームがGDDR3といった使い分けが当初はなされていたが、ほどなくこのあたりはごちゃごちゃになってしまった。

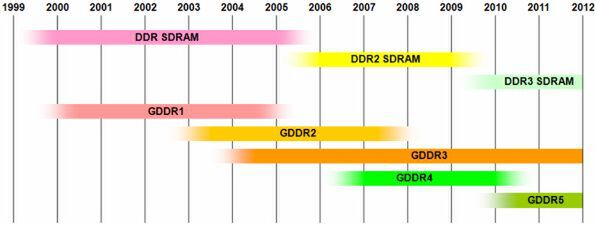

価格的にもほとんど差がなくなった結果、GDDR2は2008年あたりにフェードアウトした。一方のGDDR3は、現在でもローエンド~メインストリームの下の製品向けに利用されている。

GDDR4

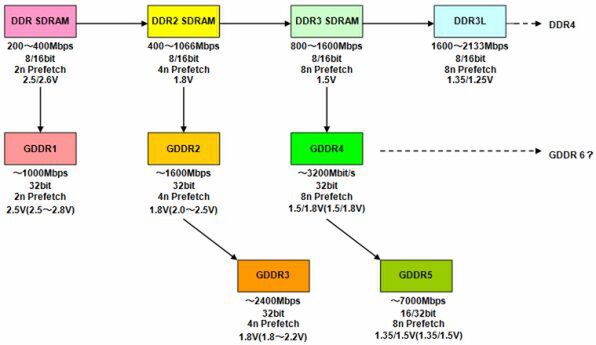

GDDR3まではDDR2をベースとしたものだったが、GDDR4はDDR3をベースとした規格に変わった。GDDR4が標準化されたのは2005年12月のことで、搭載製品が登場したのは2006年以降となっている。

基本的にはDDR3と同じ転送プロトコルを使うGDDR4だが、独自に拡張されたものとして「DBI」(Data Bus Invention)と「Preamable」がある。前者は、例えば信号が「High」の状態が連続してある程度続く際には、Highを「Low」にして送るというもので、これにより信号の駆動電力削減が可能になる。後者はレイテンシーをあらかじめ通知する仕組みで、これによりコントローラー側が効率よく通信できるようになる。

信号電圧/動作電圧は共に1.5Vと1.8Vが標準化されており、当初は1.8Vを使う製品が多かったものの、後期は1.5Vの製品が増えている。最終的には3.2Gbpsまで動作速度が上がったところで、後継となるGDDR5と入れ替わり、現在ではほとんど使われていない。

GDDR5

現役のGDDR5は、2009年9月にJEDECで最初の標準化が行なわれた。当初は4Gbpsの規格だったのが、5Gbps、6Gbpsと段々性能が上がっていき、現在は7Gbpsの量産に向けてベンダー各社の作業が進んでいるという状態である。

GDDR5はGDDR4同様に、DDR3をベースとしたものであるが、GDDR4との相違点としては、クロック信号が追加された点が挙げられる。例えば4GbpsのGDDR5の場合、1GHzの「CK」「CK#」というクロックと、2GHzの「WCK」「WCK#」という、4種類のクロック信号を使っている。アドレスやコマンドなどの転送はCK/CK#で転送し、データの書き込みはWCK/WCK#に同期させて行なうという仕組みだ。

GDDR5も当初は1.5V駆動だったが、最新プロセスを使った製品の中には1.35Vのものも登場し始めている。

ここまでの各製品が使われていた時期をまとめたのが、図4となる。

2012年以降が不透明な次世代GDDR

さて、問題は今後の話である。GDDR5で7Gbpsまで引っ張ったことで、2011年に登場するAMD/NVIDIAの製品も、引き続きGDDR5を使うことはまず間違いない。だが、2012年の世代になると、さすがに帯域が不足する。そこでより高速な転送速度(8Gbps以上)を狙うことになるのだが、この際に問題となるのが、DRAMそのものではなくGPUとDRAMの接続方法である。

GDDRとメモリーの接続は、1対1でつながるポイント・ツー・ポイント方式ではあるが、信号方式は単純なシングルエンド方式(基準値より電圧が高いと1、低ければ0)なので、さすがに正確な信号伝達が難しい領域に入っている。RAMBUSは「GDDR5で最高12Gbpsまで転送可能」というメモリーコントローラーをデモしているが、これはRAMBUSが特許を持つ技術をふんだんに盛り込んで可能になった。これと同等のことを、一般的なメモリーコントローラーで(RAMBUSの技術を回避しながら)実現するのは、かなり困難である。

これは信号をディファレンシャル(差動)方式にした場合も同じだ。やはりRAMBUSが「XDR DRAM」や「XDR2 DRAM」で山ほど特許を取得しているので、これをうまく回避しないとFB-DIMMの二の舞になってしまう。

4月あたりからJEDECは、次世代GDDRに関する話し合いを正式に始めているが、今のところ「こうなる」という確たる見通しが立っているわけではない。DRAMの内部そのものはこれまでと同じく、DDR4をベースに高速化というあたりではないかと思われる。だが、信号方式を今のままシングルエンド方式でがんばるのか、ディファレンシャル方式に変えるのか、というあたりの検討からやり直しているので、何らかの方向性が見えるまでにはもう少し時間が掛かりそうだ。

ということで、次回では次世代GDDRに大きな影響を与えているXDR DRAMについて解説したい。

この連載の記事

-

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 - この連載の一覧へ