11月19日、米EETimesはMythicが初のAIプロセッサー搭載M.2カードをリリースしたことを報じた。このM.2カードに搭載するM1108というプロセッサー(最近同社はAMP:Analog Matrix Processorと称している)、なんと性能は35TOPSである。

連載583回で紹介したQualcommのCloud AI 100の場合、Dual M.2構成のものが50TOPS以上とされているから、(こういう計算が正しいかどうかはともかくとして)M.2 1スロットあたり25TOPS以上ということになり、MythicのM1108はこれを上回る性能を実現していることになる。問題はQualcommのような資金力のある大手ではなく、スタートアップ企業でしかないMythicがこれをどう実現したかという話である。

商業的に成功した例がない

Compute-in-Memory型アーキテクチャー

Mythic, Inc.は2012年にテキサスで創業したスタートアップである。スタートアップと言いつつ直近では100名を超える従業員がいるし、拠点もテキサスだけでなくRedwood Cityにオフィスを構えるまでになっている。

Redwood Cityは、シリコンバレーの北にあたり、かつてはシリコンバレーの「外」扱いされていたが、最近はシリコンバレーの範囲がサンフランシスコあたりまで広がってる関係で、いつの間にかシリコンバレーの中になっている。物理的にはOracleの本社のご近所にあたる。

そのMythicは、Linley Processor Conference Fall 2019において創業者兼CTOのDave Fick氏が“A Graph-Based Dataflow Architecture for Executing Neural Networks”という講演を行なっている。この時に講演した同社のIPU(Intelligence Processing Unit)が、その1年後である今年11月に製品としてリリースされた、というのが冒頭の記事である。シリコンの製造や製品出荷の手前でつまずくスタートアップが少なくないだけに、ここまで来たのは大きな進展である。

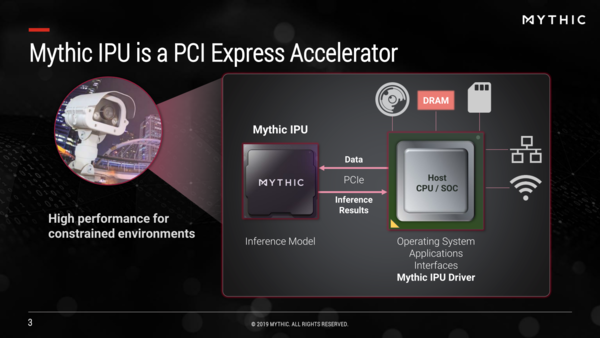

さてそのMythicのIPUであるが、大きな構造は下の画像にあるような形だ。ホストとはPCI Expressで接続され、画像なり何なりの推論元データがホストから送り込まれ、IPUからは推論結果が返ってくるという形だ。

問題はこの中身である。MythicはこのIPUに3つの要素をブチ込んだ。

- Compute-in-Memory

- Dataflow Architecture

- Analog Computing

このうちDataflow Architectureは、連載568回のWave Computingの回で説明したので割愛するとして、残りの2つ。Compute-in-Memoryは、それこそ80年台から出ては消え、出ては消えしているアーキテクチャーである。連載568回の冒頭にもあるが、要するにCPU内部の消費電力を子細に分析すると、例えばFP64の演算であっても、演算そのものに要する電力よりも、演算のためにデータをメモリーなりレジスターなりから演算器にコピーし、結果を書き戻すという「データの移動」に要する電力の方がはるかに大きいという話である。

これは従来型のCPUの構造では、多少改良することはできても大きく削減するのは難しい。ところが、メモリーと演算器を一体化してしまい、「演算は自身のメモリーセルとしかしない」と制約をつけてしまえば、演算に要する消費電力が大幅に削減できるというわけだ。

これがIn-Memory Computingの基本的な考え方である。実際、この構造を利用してメモリーセルに簡単な演算器を組み合わせたDRAMや、メモリーセルに1bitの演算器を組み合わせたMemory Cell Matrix(というよりConnection Machineの親戚というべきか)などが過去に発表されている。

ただこの方式で商業的に成功した例はこれまでない。1つはこの方式は必然的にMassive Parallel Processor(大規模並列処理プロセッサー)ということになるから、逆に演算器1つ1つは、そんなに難しい処理はできないことになる。なので複雑な演算を行なう場合、結局複数セルの演算器を組み合わせて処理することになり、こうなると途端に効率が落ちる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ