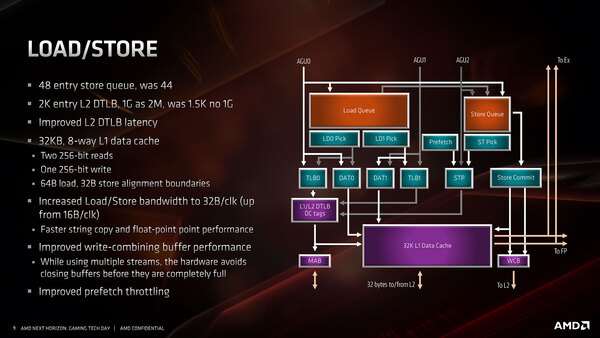

新たにAGU2制御を追加した

Load/Storeユニット周り

ALUに関しては今回特に言及がなかった。ということで、次はLoad/Storeユニットになる。以前の構造と比較するとわかるが、以下のような違いがある。

- 新たにAGU2からの制御が追加された

- Store Pipe Pick周りの構造が少し変わった(Store Pipe Pickはプリフェッチからのデータは参照しない。プリフェッチは直接STP:Store Pipeにリクエストを出す)

ちなみに3つのAGUであるが、以前は2つのAGUについて、Storeに関してはAGU0ないしAGU1からStore Queueにリクエストを出すだけだった。

| AGU0 | 基本はLoadでTLB 0/Data 0に直接アクセス可能。ただStore Queueにリクエストを出すこともできる。 |

|---|---|

| AGU1 | やはり基本はLoadで、TLB1/Data 1に直接アクセス可能。ただStore Queueにリクエストを出すこともできる。 |

これがZen 2ではAGU2が新たに追加された。

| AGU2 | 基本はStoreで、Store Pipeに直接アクセス可能。ただLoad Queueにリクエストを出すこともできる。 |

|---|

これを利用して、AGU0/1がLoad、AGU2がStoreをそれぞれ発行することで、256bit Load×2と256bit Store×1が同時に発行できるようになった形だ。

ただLoad/Store Queue経由では、かならずしもAGU0/1がLoad、AGU2がStoreである必要はなく、その意味ではインテルのAGUに比べると柔軟性は高いと言える。

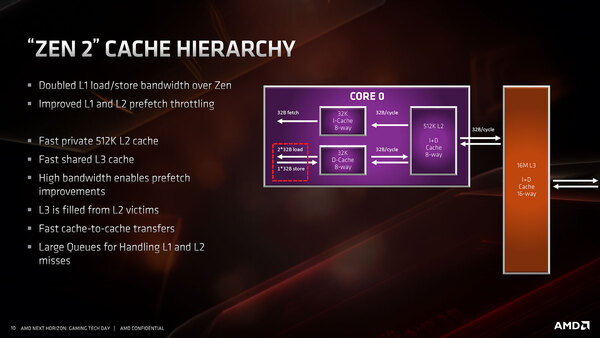

広帯域になったキャッシュ周り

さて、次がキャッシュ周りだ。Zen 2では1次/2次/3次キャッシュがすべて32Bytes/サイクルで接続されるという、けっこう広帯域な構成になっている。

ちなみに1次/2次キャッシュはSharedだが、2次/3次キャッシュはVictimの構成になっているのは従来と同じ。余談ながら、このVictimキャッシュが理由で、3次キャシュへのプリフェッチの機能は実装されていないそうである。

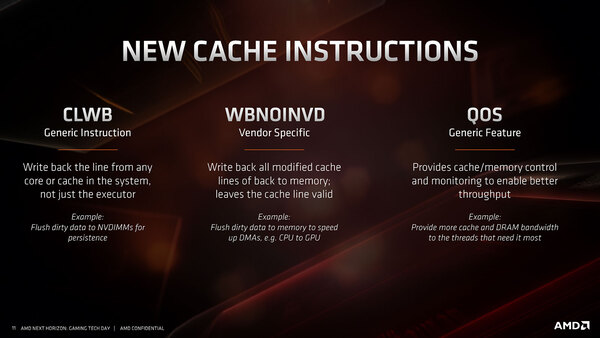

キャッシュ周りでは、3種類の制御命令が新たに追加されている。これは性能改善というよりは、例にもあるようにNVDIMMやアクセラレーター、あるいは将来のOSの利用に向けたもので、どちらかといえばRyzen系列というよりはEPYC系列向けの機能と言えよう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ