USB 3.2で配線が大幅に変更

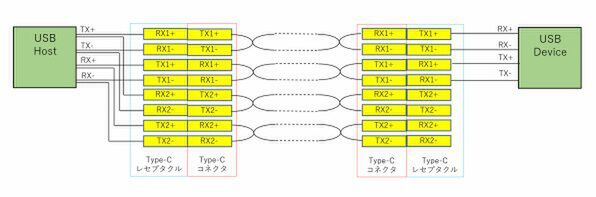

USB 2.0/3.0/3.1についてはそもそも信号が1セット分しかない。このため配線は下図のようになっている。

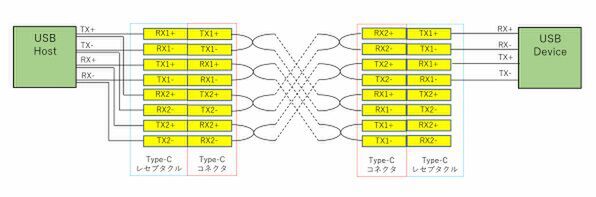

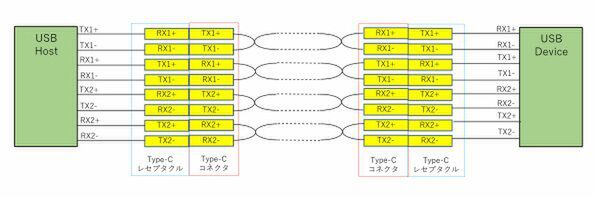

USBホストは、接続時にTX1/RX1とTX2/RX2のどちらにUSBデバイスがつながっているかを検知し、つながっている方と通信するという仕組みだ。上図の場合はTX1/RX1側を利用して通信するわけだが、下図のように仮にデバイス側のコネクターが裏返しに差されていた場合、今度はTX2/RX2側を利用して通信する仕組みとなる。

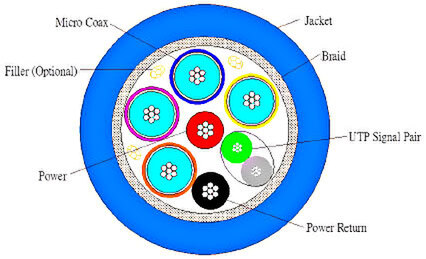

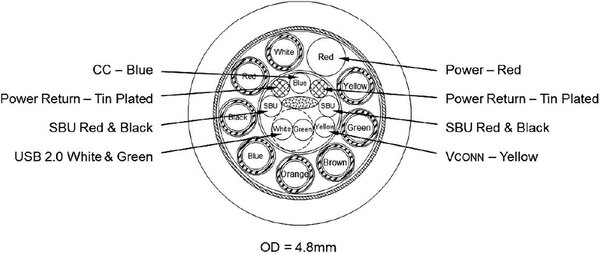

そこで配線そのものも大幅に変更になった。下の画像はStandard/Micro USBと、USB Type-Cケーブルの断面図であるが、配線そのものが大幅に増えているのがわかる。

画像の出典は、USB 3.1 Legacy Cable and Connector Specification Revision 1.0

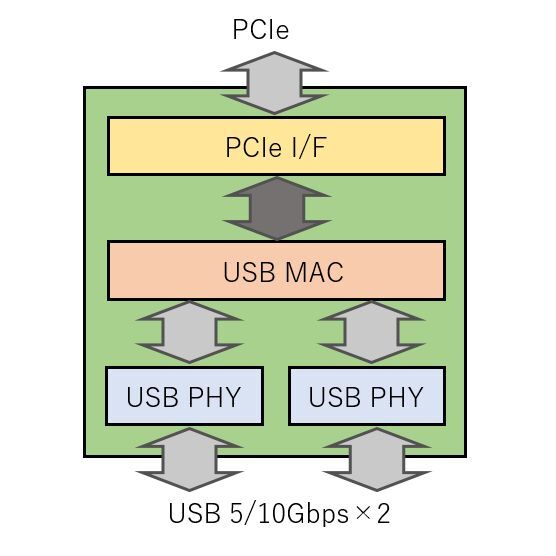

さて、話はUSB 3.2である。USBは2レーンオペレーションと言っており、要するにこれからは下図のようなつなぎ方になるわけだ。

コネクターが裏表逆になると、その側はTX1とRX2/TX2とRX1がそれぞれつながるような形になるが、もともとTX1/RX1とTX2/RX2は単に配線などの都合上番号を振っているだけで、必ずしも1と1がつながらなくても問題はない。ただこうした構成にしたことで、コントローラーの構造に変化が生まれることになった。

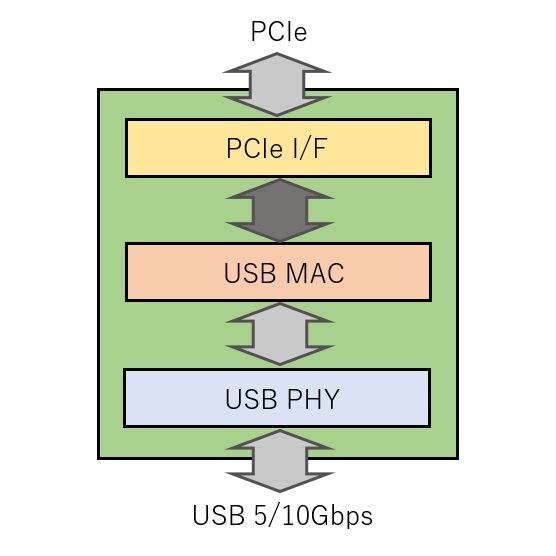

下図は従来のUSB 3.1までの構造である。ホスト(CPUなりチップセットなり)とPCIeのI/FでまずUSBのMAC層がつながり、その下にPHY(物理層)がつながり、その先にUSBが出てくるわけだが、USB 3.2の2レーンオペレーションでは、PHYが2つという構成になった。

信号速度は相変わらず5Gbpsないし10Gbpsであるが、それが2組出る形だ。ちなみにUSB 3.1までの互換モードで動作する場合、2組のPHYのうちの片方のみが動作し、片方は休んでいる状態となる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ