プロセッサーの構造を大幅に変更

プロセッサーの構造そのものが大幅に変わるのは、次のSystem z10である。当初このSystem z10のCPUはIBM z6と呼ばれていたが、最終的にz10プロセッサーとなっている。なぜz6だったかというと、POWER6と設計情報をだいぶシェアしているためだ。

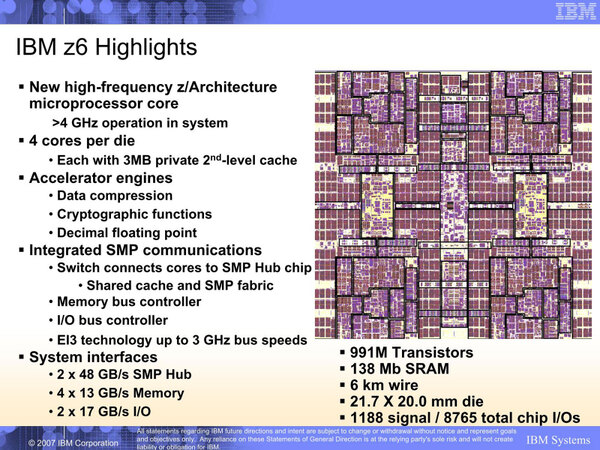

コアは4GHzオーバー(最終的には4.4GHz)で動作し、それぞれ独立した2次キャッシュを持つ構造で、1ダイあたり4コアの構成となる。

画像の出典は、IBM z6 - the next-generation mainframe microprocessor

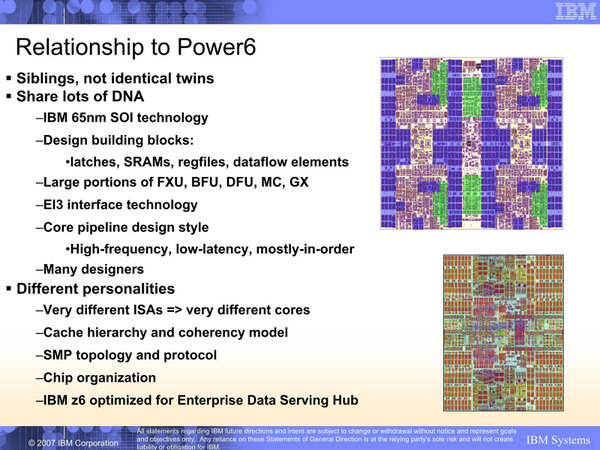

ちなみにPOWER6との比較が下の画像で、コンポーネント(ラッチとかSRAM、レジスタファイル)の論理構造や物理構造のほか、基本的なパイプラインの「考え方」が共通とされる。

画像の出典は、IBM z6 - the next-generation mainframe microprocessor

その一方で、そもそも命令セットが異なるので、当然ダイは異なる。またz6は1ダイに4コアの構成だったが、POWER6は1ダイあたり2コアの構成である。ただ命令セットが異なると言いつつも、さすがにCISCをそのまま実装するのではなく、CISCの命令セットをデコード段で命令変換をかけてRISC風にし、これを処理するという昨今のx86と同じ実装方式になっている。

パイプラインは14段であるが、POWER6が7命令同時発行のスーパースカラー+SMT(Simultaneous Multithreading:同時マルチスレッディング)という構成なのに対し、z6はもう少し控えめな構成で、SMTもサポートされていない。その代わりPOWER6と比較しても圧倒的に充実したRAS機能が搭載されるという具合に、狙いどころが明確に異なるものに仕上がっている。

このz6(のちにz10に改称)プロセッサーを搭載したSystem z10 Enterprise Class(EC)は2008年2月に発表された。プロセッサ数は最大64に増強され、z990ベースのシステムと比較して1.5~1.6倍高速とされた。

また同じ2018年の10月には普及帯向けとして動作周波数を3.5GHzに絞り、プロセッサー数も減らしたSystem z10 Business Class(BC)も追加されている。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ