微細化すると寿命が縮むため

メモリーを縦に積むことで容量を稼ぐ

セルの寿命の短さを助長しているのが、微細化である。冒頭のスライド画像に戻ると、容量を増やすためにものすごい勢いで微細化を進めているのがわかると思う。

ところで、微細化というのは、セル全体の寸法をそのまま縮めるという意味であり、すると必然的にトンネル酸化膜も薄くなっていく。ということは、その分早く酸化膜が寿命を迎えるという意味であり、これがそのまま寿命の短縮につながることになる。

また微細化そのものも、このところ頭打ち気味であり、容量は増えないわ寿命は縮まるわ、しかしながら大容量化への要望は激しいわ、ということでフラッシュメモリー業界が考えたのは「それでは縦に積みましょう」という策だ。

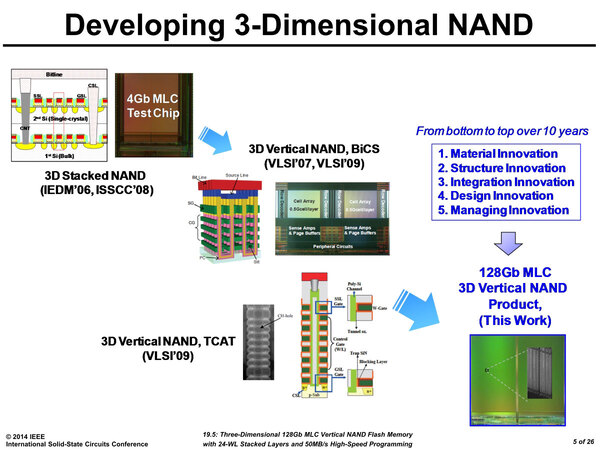

最初は文字通り、素直に複数のフラッシュメモリーを縦積みして、間をTSV(Through Silicon Via:シリコン貫通電極)でつなぐというもの(下の画像の左上)だった。

画像の出典は、SamsungのISSCC 2014における論文より”

これだと確かに容量は稼げるものの、コスト削減にならない(前回も触れたがTSVを構築する分、むしろコストが上がる)ので、根本的な解決にならなかった。

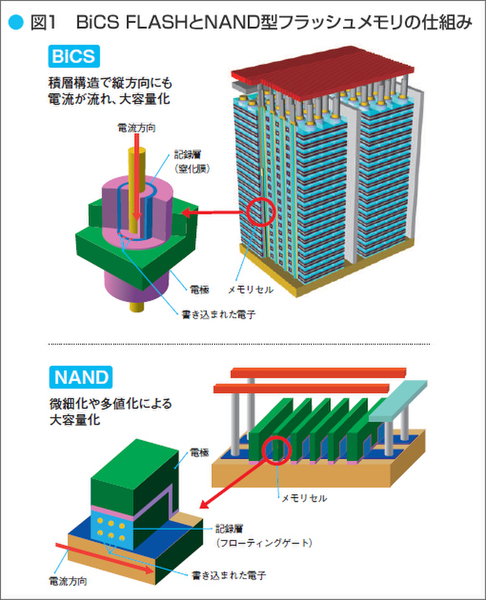

そこで、2次元構造のFlashのセルを縦積みにするのではなく、根本的に3次元構造のセルを開発しましょう、という話になった。これに基づいて2007年に東芝が発表したのがBiCS(Bit Cost Scalable) NANDである。

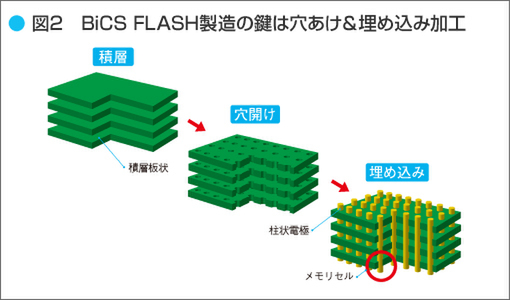

BiCSの構造の概略は東芝のウェブサイトに掲載されているが、要するに縦方向にセルを並べる構造で、セルそのものも円筒形になっている。

画像の出典は、“東芝科学館”

この構造をBit Cost Scalableと呼ぶのは、製造コストが抑えられるからということだ。

画像の出典は、“東芝科学館”

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ