多くの企業に採用された先進的なチップセット

C-Bus II

C-Bus IIは64bit幅で、バス帯域は400MB/秒となっているので、バスクロックは50MHzほどになる計算だ。おそらくは共有バス方式を取っており、1つのC-Bus IIに最大4つまでプロセッサーを搭載できる。このC-Bus II同士を最大4本まで1つのシステム内で接続できる構成になっていたと思われる。

またPentiumそのものはBusにECCが出ていないが、C-Bus IIはバス自身にECCのサポートが付き、またメモリーもECC付きを標準でサポートしている。

さらにC-Bus IIには192Byteと非常に小さいながら高速なキャッシュが搭載され、これは排他的キャッシュ(Victim Cacheとも呼ばれるが、AMDがK8世代で使っていたアレだ)構成で、システムから見ると3次キャッシュとして動作した。

メモリーはシステム全体で3GBまでサポートしており、バスプロトコルはライトバック方式のキャッシュコヒーレンシをサポートするという、なかなか先進的な構成であった。おまけにバスの電気的特性としては、P6バスよりも早くGTL(Gunning Transceiver Logic)を採用している。

GTL自身は、XeroxのWilliam Gunning氏が1991年に開発したもので、JEDEC標準にもなっている規格であるが、早くからこれを採用したことの意義は大きい。ちなみにP6バスには、このGTLを改良したGTL+(改良を行なったのはFairchild Semiconductor)が採用されている。

特徴的なのはこのC-Bus IIは、SCSI/PCI/EISA/MCAの各バスとのI/Fをサポートしていることである。PCI/EISA/MCAはわかるのだが、直接SCSIへのバスブリッジが出るインターコネクトというのは、筆者は初めて見る。

またOSとしてはIBMのOS/2 SMP、Windows NT Server、Novell Netware、SCO Unix Ware、SCO UNIX/SCO MPX、Sun Solarisがサポートされており、すべてのOS環境でSMP構成を利用可能だった。

このC-Bus IIは、3種類のライセンス形態があった。1つは完全にカスタマーが自作する場合で、この場合500ドル払うだけで完全なバスプロトコルの仕様書を入手できた。

もう少し楽をしたいという場合、Corollaryが提供するC-bus II ASIC(SIMPL Chipset)を購入し、これでシステムを構築できた。このC-Bus II ASICにはCBC(Cache Bus Controller)、DPX(Data Path Exchange)、PCIB(PCI Bridge)、CMC(Cache Bus Memory Controller)の4種類から構成されている。

もっと楽をしたければ、C-Bus II Board Level Productと呼ばれるボードも同社は提供した。CBII/6000という型番の製品があったことはわかっているのだが、こちらの具体的な構成や写真などはついに手に入らなかった。

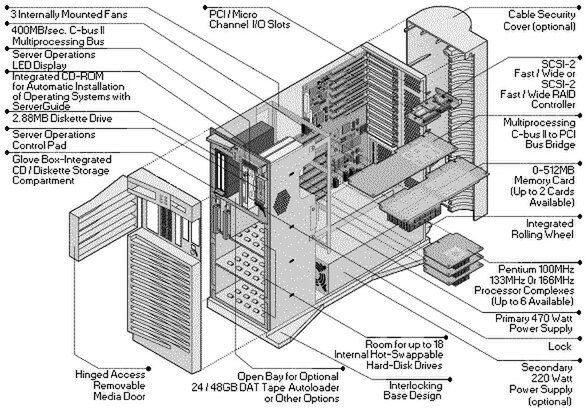

ただ通常サーバーメーカーは、2番目のチップセットを購入して自社でサーバーを組み上げる選択をした。代表例の1つは、IBMが1996年に発表したPC Server 720であろう。このマシンはPentium 166MHzを最大6Pで構成できるというもので、タワー型のシャーシに最大6枚のプロセッサカードと7枚の拡張カードを搭載できた。

画像の出典は、“IBM EPRM”

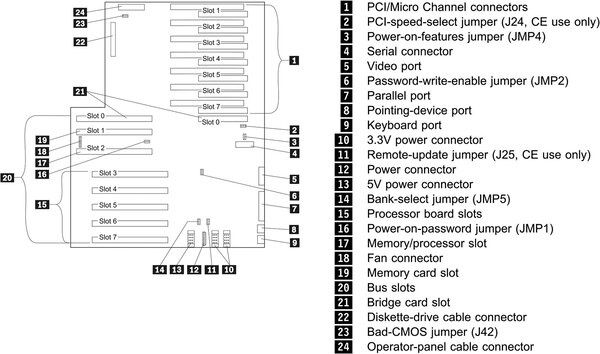

画像の出典は、“IBM PC Servers Hardware Maintenance Manual Marchi 1996(S30H-2501-01)”

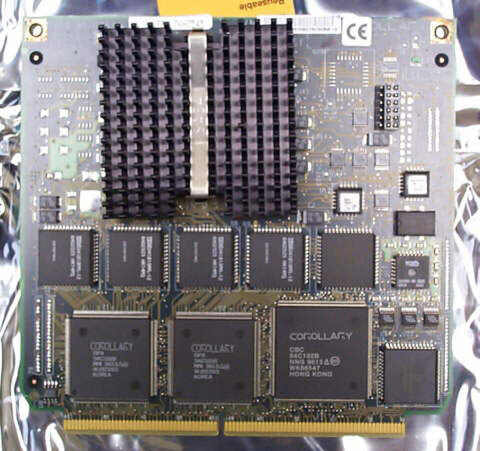

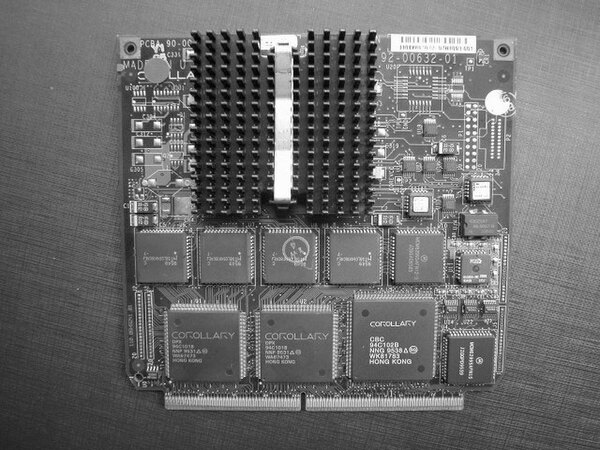

肝心のプロセッサーカードが、下の画像だ。微妙に2枚のカードで配置が異なるが、76H3545と76H3248という2種類のカードがあったようで、下のカラー画像が76H3545、モノクロ画像が76H3428なのではないかと思われる。

画像の出典は、“ICD, Inc.”

画像の出典は、“Pentium "antichi" o particolari”

このC-Bus II製品は結構なヒットになり、Data General、富士通、日立、IBM、Intergraph、NEC、Olivetti、CHEN Systems(連載346回に出てきたSteve Chen博士の会社だ)、Samsung Electronicsといった多くの企業に採用されるに至る。

ちなみにC-Bus IIは上に書いたように最大16プロセッサーまでサポートしていたが、実際に販売された構成は8プロセッサーが最上位だったようだ。

Data GeneralのAViiON Enterprise Servers model 5800やNEC Express 5800/170などいくつかの採用例はあるが、これを超える規模はそろそろ共有メモリー方式では厳しいという判断だったらしい。この教訓は続くProfusionに生かされることになる。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ