QCDOCのベースは

PowerPC 440

こうした背景を元に、1997開発されたQCDOCは、PowerPC 440をベースとした、非常にコンパクトなマシンになった。PowerPC 440そのものはIBMが1999年に発表した、組み込み向けのPowerPCコアである。

組み込み向けというのは、単にCPUパッケージとして組み込み機器に入れる以外に、ASIC(特定用途向け専用IC)内部に統合することも想定していることを指す。

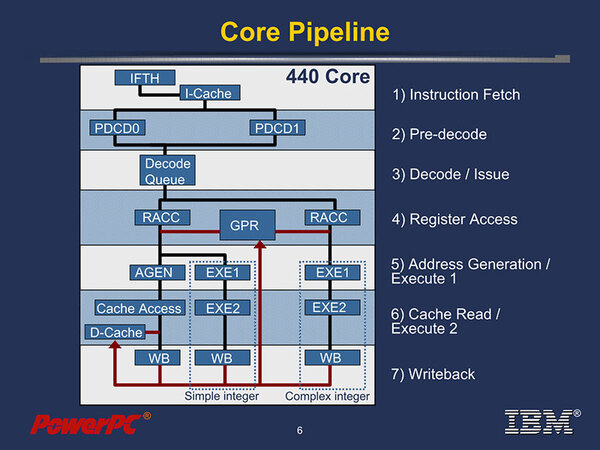

内部は2命令同時実行のIn-Orderスーパースカラーで、パイプライン段数は7段という比較的おとなしめのスペックになっている。

性能は、Dhrystone 2.1で1.8MIPS/MHzというあたりだ。ただし組み込み向けということで、消費電力はIBMの180nmプロセスを使った場合で2.5mW/MHzと、かなり少ない。

QCDOCの場合は500MHzで動作したので、稼動時のCPUコアの消費電力は1.25Wほどでしかない。またトランジスタ数は32KBの命令/データキャッシュを込みで550万個、ダイサイズは、これもCPUコア部だけで言えば同じく180nmプロセスを使ってわずか4mm2に抑えられている。

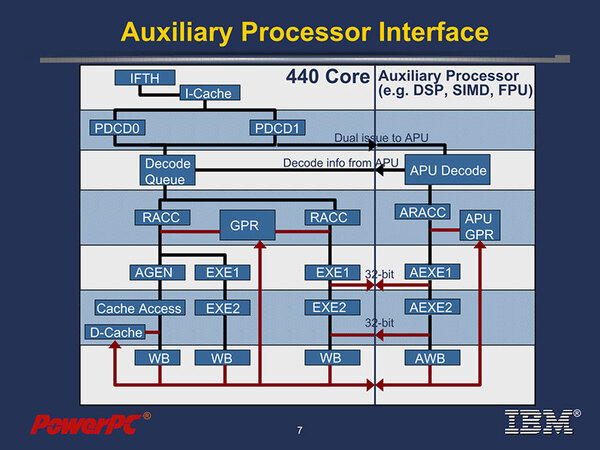

ところが、PowerPC 440そのものは整数演算ユニットのみで構成されているので、このままでは科学技術演算には不利である。そこで、特にSoCを利用する場合に向けてAuxiliary Processor Interfaceなるものが用意されている。

このインターフェースを使ってFPU(Floating Point Unit)を追加することで、浮動小数点演算を高速にすることも可能となっている。

QCDOCは部品点数を抑えて

低コスト化を実現

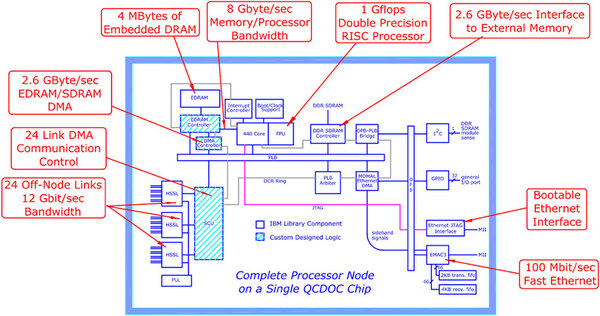

下の画像がQCDOCの内部構造である。PowerPC 440コアに、倍精度のMAC演算が可能なFPUを組み合わせ、さらにローカルで4MBのEmbedded DRAM、DDR SDRAMのI/F、Network×2などを組み合わせたうえで、独自のSCU(Serial Communication Unit)を搭載して、24本のリンクが出せるようになっている。

ちなみにイーサネットそのものはあくまで起動あるいはシステム管理用で、これを使ってプロセッサー間通信を行なっているわけではない。

上の画像で白い部分はIBMがIPとして元々持っていた部分で、水色の斜線部のみQCDOCにあわせて新規に開発された部分である。そんなわけで、ほとんどの部分は既存のIPを流用して作られたわけだ。

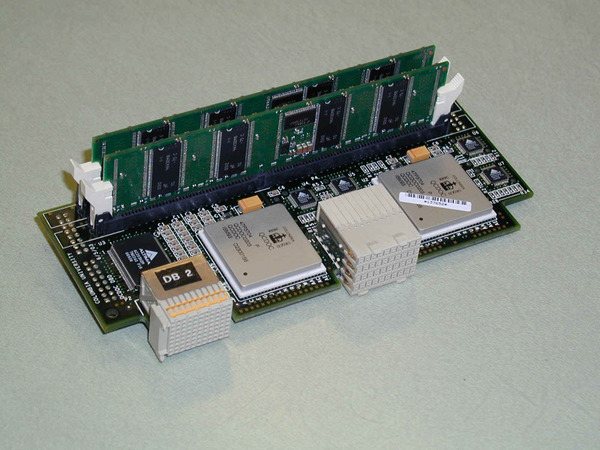

ちなみにQCDOCチップも、やはりIBMのCMOS 7SF(180nm CMOS)で製造されている。このチップを2つ搭載したカードが下の画像である。

QCDOCの場合、初期コストの低減も重要な課題であり、DDR SDRAMとイーサネットのPHY以外はほぼすべてがQCDOCのチップの中に収められており、部品点数が非常に抑えられ、ひいてはコスト削減にもつながる。このカードもQCDSP同様に、32枚(64ノード)をまとめて装着できるボードの形で実装されている。

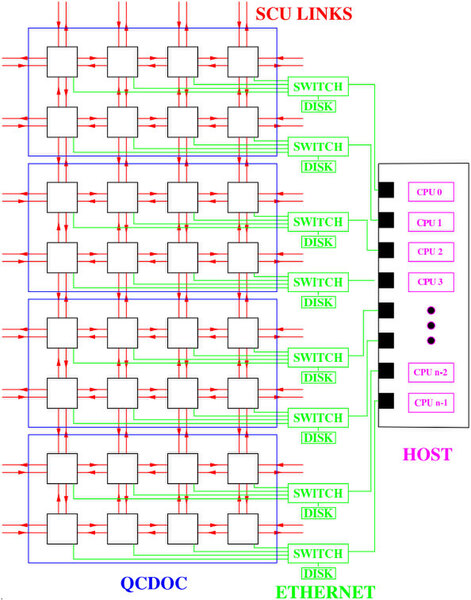

ノード間接続は、6次元のトーラス構造である。下の画像は小規模なQCDOCを使った4次元構造の例だが、台数が多くなる場合は平面構造を複数枚積み重ね、間をやはりSCUリンクでつなぐ格好になる。

リンクの速度は500Mbpsで、ノード間のレイテンシーは50ナノ秒前後とされる。帯域そのものはそう早くないが、レイテンシーは比較的少なめであり、またリンクから直接EDRAMやSDRAMをアクセスするためのDMAエンジンも搭載されるなど、色々工夫がなされていた。

→次のページヘ続く (ASCプロジェクト関係者が注目するほどの価格性能比)

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ