2015年のロードマップは未公開

デスクトップ向けはやめる?

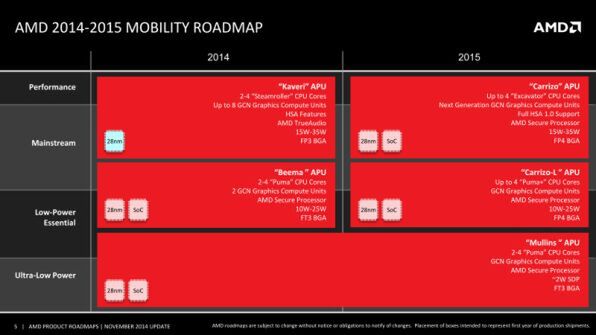

デスクトップ向け製品がリリースされるか怪しくなってきたことに拍車をかけたのが、2014年11月に同社が公開した製品ロードマップである。モバイル向けは、Kaveriに替わりCarrizoが投入されることが明確にここで示された。

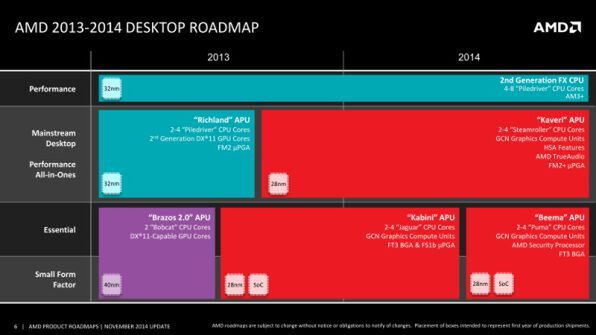

しかし、デスクトップ向けは2015年のロードマップが示されないままであった。これで「AMDは2015年にはデスクトップをやめるのではないか」といった観測まで飛び交うようになった。

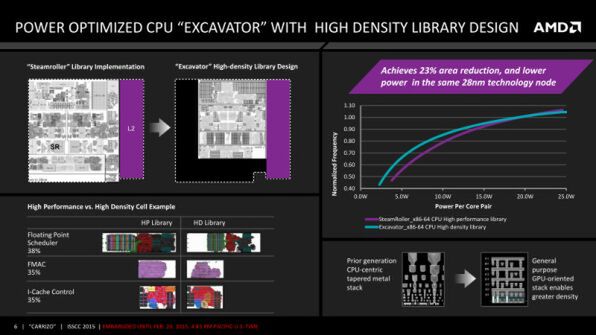

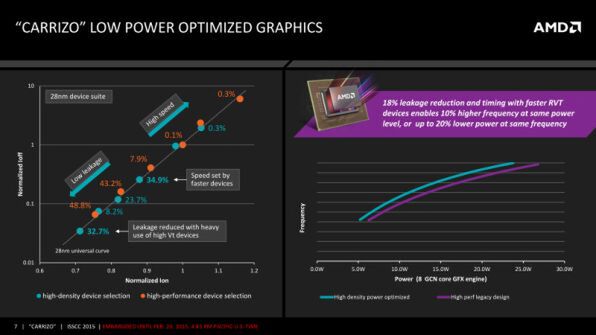

トドメを刺したのが、2015年2月に開催されたISSCC(international Solid-State Circuits Conference:国際半導体回路会議)である。AMDはここでCarrizoの詳細を公開した(関連リンク)。

会議の名前にふさわしく、ここでは製品そのものというよりは、その製品の内部回路の実装方法が発表されたわけだが、AMDはここでCarrizoの設計が、KaveriをベースにHigh Density Libraryを利用したことと、低リークのトランジスタを多用したことを明らかにした。

性能と消費電力のどちらを重視するかは

Cell Libraryの数で決まる

内部回路についてはもう少し説明が必要だろう。連載237回でロジック回路の解説をした時には省いたのだが、例えばここで紹介したAND回路を内部に1個入れようと思った場合、設計者はいちいちトランジスタを追加して配線を……なんてことはしない。

実際にそれをやれば、最大限の高速化と最大限の回路節約ができるのだが、設計の手間も最大限になってしまい、現実的ではない。その代わりに、Cell Library、あるいはStandard Cell Libraryと呼ばれるものがファウンダリーから提供されるので、これをつなぎ合わせることで目的の回路を実装する形になる。

このCell Libraryと呼ばれるものは、実態としては「回路ブロックの塊」である。つまりAND/OR/NOT/NAND/NOR/XORといった一番基本的なレベルのロジック回路だけでなく、それを組み合わせてLatch/Counter/Adderなどのもう少し上位レベルの機能も提供してくれるものである。

Cell Libraryは通常、いくつかのバージョンが用意される。大雑把に言えばCell Libraryは通常トラック数なる数字で示されることが多い。Cell Libraryは物理的には長方形をしているが、この長辺(か短辺かは状況によって多少差があるが、通常は長辺)の長さ、正確に言えばその長辺につながっている配線の数である。

9トラックといえば9本の配線が並んでいる形で、12トラックといえば12本である。このトラック数は以前は15トラックなどもあったらしいが、最近は7.5/9/10.5/12トラックあたりが一般的である。

このトラック数が多いと、1つのCellに多くの機能を詰め込みやすいため、一定の機能を盛り込むために必要なCellの数が減り、結果として高速化につながる。これはパイプライン処理を考えるとわかりやすい。

パイプライン処理を構成する場合、パイプライン1段の処理時間が短いほど高速化が可能であり、そのためにはパイプライン1段の回路を減らすことが効果的である。トラック数の多いCellを使うと、トータルとしてのCell数を減らせるため高速化に有利である。

ただしその一方で、Cellが大きいということは、必ずしも複雑な処理が必要ない場合でも大きな面積を占めることになるので、面積的に無駄が多い。また面積が多いというのは配線長が増えるということであり、配線に起因する消費電力が増えることになる。

逆にトラック数が少ないと、1つのCellに盛り込める機能がやや減ることになり、複雑な機能を実現するためのCell数は増えることになる。これはパイプライン処理を考えた場合、トータルのCell数が増えることになるので、高速化にはやや不利である。

その一方、トラック数が多いCellよりも面積を有効活用するので、面積的な無駄は減るし、これにともない配線に起因する消費電力は減る。ということで、性能とダイサイズ/消費電力のどちらを取るかでトラック数を選ぶことになる。

→次のページヘ続く (Carrizoがデスクトップ向けに導入される可能性)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ