OSの移植を容易にするプロセッサー

EV4こと「Alpha AXP 21064」

最初に登場したのが「Alpha AXP 21064」チップで、通称EV4と呼ばれる。EVは“Extended VAX”の略で、4は利用したプロセスノード(CMOS-4:0.75μm)を示す。これに先立ち、EV3というCMOS3(1.0μmプロセス)を利用したテストチップも製造されたが、こちらはダイサイズの制限もあってか、FPUを持たない設計になっており、量産には至らなかった。

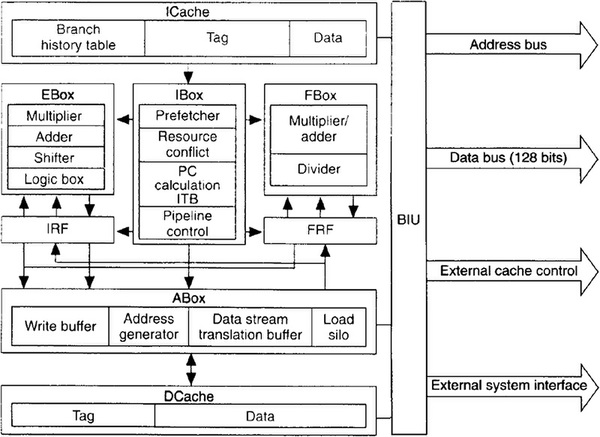

そのEV4の内部構造は下の画像のようになっている。命令デコードを行なうIBoX、整数演算を行なうEBox、浮動小数点演算を行なうFBoxとアドレス制御を行なうABoxという4つのブロック、それにキャッシュとレジスターファイルから構成される。

ダイ寸法は14×17mmの238mm2、トランジスタ数は168万個と発表された。動作周波数は最大200MHzで、これは当時としてはかなり高速な部類に入る。

命令セットは独自のもので、VAXとの互換性はない。そもそも64bitに拡張した時点で命令の互換性を保つのは難しいが、それにも増してVAXはCISCの極北とも言うべき命令セットで、これを命令セットに持ち込んだらRISCの利点を全部潰しかねないからだ。

ただ再コンパイル(や最小の手直し)でアプリケーションが移行できるような配慮がされた。その最たるものがPALcode(Privileged Architecture Library code)で、名前の通り特権命令をカスタマイズできるものだ。

Alphaの場合、同社が提供していたVMSというOSが4レベルの保護メカニズムを必要としており、他方UNIXは2レベルで実装されていた。他にもWindows NTの移植が予定されており、こうしたOSの要求に応じて異なるPALcodeを提供することでOSの移植を容易にするという配慮がなされた。

また一部の命令はハードウェアで実装しきれず、これをカバーするためTrap barrierなる仕組みが容易されている。これはある「定義はされているが実装されていない」命令が到達した場合に発動され、通常の命令処理を中断してソフトウェアでこれを処理する、というものである。こうした機構を持つプロセッサーはAlpha以外あまりお目にかかったことがない。

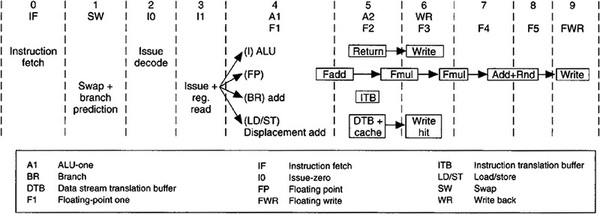

パイプラインは下の画像の通りで、整数演算と浮動小数点演算を同時に行なえるIn-Orderの2-wayスーパースカラー構成である。もっとも2命令同時実行といっても整数演算は1命令/サイクルだから、実効性能としてはやや見劣りする。

同社の資料によれば、200MHzのEV4の性能は、SPECint92が104.3、SPECfp92が200.4とされている。少し後になるが、1994年に投入されたP54CベースのPentium 100MHzがそれぞれ95.0/86.1、あるいは1994年に投入された100MHzのPowerPC 604がそれぞれ105.9/108.2というスコアを出しており、動作周波数との比を考えると浮動小数点演算性能はともかく整数演算性能は十分とは言えなかった。

そこで、1993年10月に発表され、1994年に投入されたのがEV45ことAlpha AXP 21064Aである。こちらはプロセスをCMOS5(0.5μm)に微細化し、キャッシュサイズを命令/データともに16KBに増量。さらにFPUの性能改善や分岐予測ユニットのバッファ拡充など細かく手を入れ、同時に動作周波数を最大300MHzまで引き上げることに成功する。

EV4の倍の規模のスーパースカラー

EV5こと「Alpha 21164」

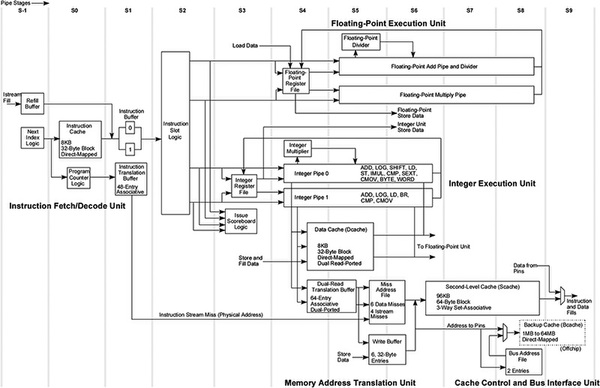

1995年には、後継としてEV5こと「Alpha 21164」(AXPはもうこの頃付かなくなっていた)が投入される。4命令同時実行というEV4の倍の規模のスーパースカラーとなっているのが最大の特徴である。

これにより整数演算性能を大幅に引き上げ、浮動小数点では加算と乗算が同時に行なえるようになったので、MAC演算が見かけ上1サイクルで実施できることになった点も大きい。

ちなみにEV5そのものは最大333MHz(当初は300MHzという発表だった)駆動とされたが、この後継としてEV56が1995年末に発表され、1996年から量産される。こちらはプロセスをCMOS5(0.5μm)からCMOS6(0.35μm)に微細化したバージョンで、最大動作周波数は700MHzに達した。

SPEC CPU 95の結果を見て見ると、612MHz駆動のAlpha 21164はSPECint95 18.4/SPECfp95 20.8というスコアが示されている。この結果のテスト時期(1997年9月)に近いものを探すと、インテルのPentium 233MHzがそれぞれ7.03/5.18、IBMの332MHz Power604eが12.9/6.21となっており、同世代のプロセッサーと比較して頭一つ抜け出した成績を維持できていることがわかる。

→次のページヘ続く (EV8まで続く後継プロセッサー)

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ