複数のシステムを並行して開発

順次それを利用する方法がASCI

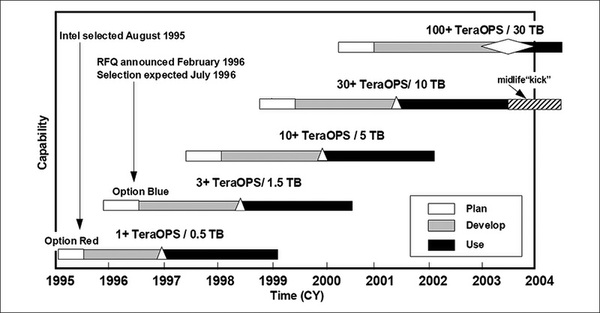

ASCIでは、目標に対して一足飛びで完成版のシステムを作るのではなく、複数のシステムを並行して開発しつつ、順次それを利用する形で目標を達成しよう、というアプローチが取られることになった。それが下の画像である。

具体的には以下の表の形で進行した。PurpleのみASCに名前が変わっているのは、2004年にプロジェクト名がASCIからASCに切り替わったためである。

| ASCIのシステム | ||||||

|---|---|---|---|---|---|---|

| Option名 | 演算性能 | メモリー量 | 実用化時期 | |||

| ASCI Red | 1T FLOPS以上 | 0.5TB | FY1996 | |||

| ASCI Blue | 3T FLOPS以上 | 1.5TB | FY1998 | |||

| ASCI White | 10T FLOPS以上 | 5TB | FY2001 | |||

| ASCI Q | 30T FLOPS以上 | 10TB | FY2003 | |||

| ASC Purple | 100T FLOPS以上 | 30TB | FY2007 | |||

ちなみにこれはあくまで当初の計画に沿った表であるが、実際にはASCI BlueはASCI Blue PacificとASCI Blue Mountainの2つが存在する。またASCI Redの後継としてRed Stormが追加された。

2000年にはASCIの各マシンを埋める位置づけとなるBlue Gene/Lも発注され、2005年に実用化された。このBlue Gene/LはIBMが独自に開発を続け、Blue Gene/PおよびBlue Gene/Qが開発された。このBlue Gene/QをベースにしたものがSequoiaとして2012年から稼動している。

これらの各々のマシンの詳細は次回から細かく説明していくとして、その前にASCIとASCプロジェクトにもう一度話を戻す。

ASCIのそもそもの目的は、冒頭に述べたとおり核実験のシミュレーションである。これについて列挙すると以下のようになる。FY2000とは、アメリカ会計年度の2000年(2000年10月1日~2001年 9月30日)を意味する。

| ASCIとASCプロジェクトの進捗 | |

|---|---|

| FY2000 | 核兵器を使っての爆発(Primary Explosion)を3Dシミュレーションするとともに、その内容を分析するというデモに成功。 |

| FY2001 | 二次爆発(Secondary Explosion)のデモにも成功するとともに、ASCI Whiteを利用しての完全に動作する問題解決環境を提供することに成功する。またシミュレーション条件に関する諸々の検証に初めてパスする。 |

| FY2002 | 完全な熱核兵器の爆発シミュレーションと、アクシデント状態での核兵器の状況の3D分析も可能になった。 |

| FY2003 | 核兵器システムの様々な状態における安全シミュレーションを提供開始。 |

| FY2004 | 実際の核兵器のモデルの検証を完了し、W76/W80核爆弾の寿命延長に向けた整備をサポートするとともに、W88核爆弾のサポートを追加。また、非核兵器の実験と判定のシミュレーションもサポート。 |

おおむね2005年頃には初期の目的をある程度達成できるようになった。これに続いて他の核兵器のサポートや、さらに新しいシミュレーションなども随時追加され続けているのだが、最初のASCIの目的はほぼ達した、と考えていい状態になった。

これを受けてASCIがASCに切り替わったのは2004年のことである。ASCの主目的は引き続きSSMP/SSPの維持であるが、加えて当初の目的にはなかった複雑かつ不確実なシナリオのサポートやICF(Inertial Confinement Fusion:慣性核融合)のサポートなど、より高度なレベルにターゲットを移し、現在も継続中である。

結果として、2009年にはPeta FLOPSマシン、2016年には100P FLOPSのマシン、2018年にはExascale(1E FLOPS)のマシンをそれぞれ必要とするというロードマップを描いていた。ちなみにPeta FLOPSマシンがCielo、100P FLOPSのマシンが先ほども出てきたSequoiaとして現在稼動中である。

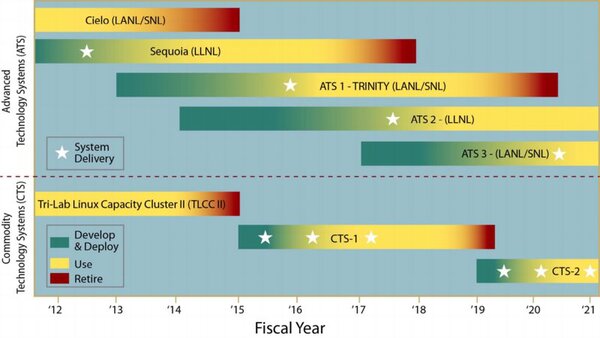

これに続き、ASCの最新ロードマップ(PDF)では、AST 1(Trinity)/ATS 2/ATS 3という3世代のATS(Advanced Technology Systems)と、それとは並行してTLCCII/CTS-1/CTS-2という3世代のCTS(Commodity Technology Systems)が開発されることが明らかにされている。

ATSというのは、SSPに向けたピーク性能を求めるスペシャルシステム。対してCTSというのは標準的なシステム構成を使って低価格で計算能力を実現しようというものである。

現在利用されているTLCC II(Tri-Lab Linux Capacity Cluster 2)は、ローレンス・リバモア、ロスアラモスサンディアの3つの国立研究所で共同で運用しているLinux Clusterの第2世代というところから来る。こちらの話もいずれすることにはなると思うが、引き続きASCは米国のスーパーコンピューターの市場を牽引し続けていると言っていいだろう。

今回は珍しくシステムの話をしないで終わってしまったが、ASCI/ASCの位置づけが複雑なので、これで1回分を割いて説明した。というわけで次回はASCI Redから順次解説していきたい。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ