CDC 1604の後継機CDC 6600は

1965年の発売当時世界最速

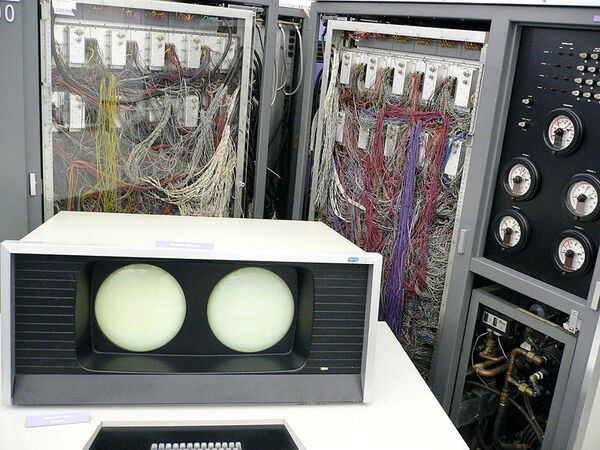

CDC 1604の後継としてシーモア・クレイが開発を始めたのがCDC 6600である。CDC 6600は1965年に発売され、初号機はCERN(European Organization for Nuclear Research:欧州原子核研究機構)に納入された。ちなみになぜ略号がEONRではなくCERNかというと、フランス語だと"Conseil Européen pour la Recherche Nucléaire"になるからである。

このCDC 6600は当時としては世界最速のマシンである。設計目標はCDC 1604の100倍で、前回のStretchを彷彿させるものがある。これを実現するために、当時Fairchild Semiconductorが発売したばかりのトランジスタを採用してシステムを構築したが、これだけでは足りなかった。

CDC 6600はひとつのプロセッサーで構成されるが、CP(Central Processor)そのものはレジスターとの間での算術命令しか行なわない、まさしくRISCに近い命令セットを取った。

では、レジスターとメモリー/外部記憶の間の処理などはどうするかというと、PP(Peripheral and Control Processors)なるものが10基相当分用意されており、演算以外の作業は全部PPが担う。PPそのものはCDC 160をベースとしたものであるが、これが10基入っているのではなく、10倍速で動き、かつBarrel and slot方式を採用している。

Barrel and slot方式とは、サイクル毎に実行するタスクを切り替えることで見かけ上複数のタスクが同時に動く方式である。所謂時分割であるが、違うのはハードウェア的に強引に実行するタスクを切り替えていることだ。最近ではXMOSのXCOREがこれである。

話を戻すと、例えばデータを読み込んで演算をして結果を書き戻す場合、以下ののような処理になる。

- PPが外部記憶からメモリーにデータを読み込む×2

- PPがメモリーからレジスターにデータを読み込む×2

- CPがレジスターからデータを読み込んで演算結果を別のレジスターに書き込む

- PPがレジスターに書き込まれた結果をメモリーに書き出す

- PPがメモリーに書き込まれた結果を外部記憶に書き出す

このように、プログラムそのものはそう書きやすいとは言えず、最適化がやや大変だったようだ。

そのCPであるが、動作周波数は10MHzながら、4相クロックを利用することで内部は4倍速の40MHz相当で動作した。さらにスコアボード方式のスーパースカラーを実装しており、命令の並列実行が可能であった。命令ユニットとしては以下の9つが用意されていて、これが全部並列で動作した。

- 浮動小数点乗算×2

- 浮動小数点除算×1

- 浮動小数点加算×1

- 整数加算×2

- Barrel Shifter×1

- 論理演算×1

- 分岐先アドレス計算×1

もっとも整数加算はもっぱらメモリーのLoad/Storeのアドレス計算向けで、分岐先アドレスは分岐がなければ意味がないが、浮動小数点演算が異様に充実していることがわかる。浮動小数点は60bitフォーマットで、加算は外から見れば4cycle(400ns)で可能だったという。つまり内部的には16cycle掛かっているわけだ。

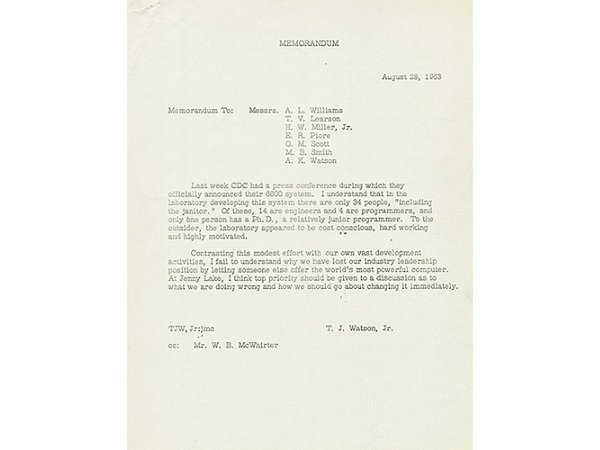

理論上の演算性能はおおむね1MFLOPS、実際にアプリケーションを動かした場合の性能は、最終的に0.5MFLOPSほどあったとされる。CDC 6600が発表された時に、当時IBMを率いていたWatson Jr.が社内に回した有名な覚書がある。

「清掃夫を含んでも34人しかおらず、しかもエンジニアは14人、プログラマは4人、博士号を持ってるのは1人しかいない研究所が作る製品が、なぜ我々の製品より性能が高いのか理解できない。我々が間違っていたのは明白で、至急是正の必要がある」

これを読めば、その性能がどう捕らえられていたかがわかろうというものだ。

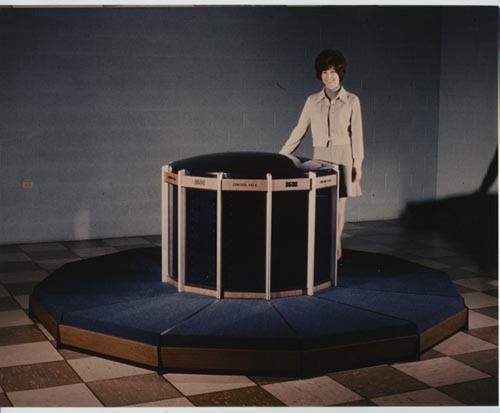

CDC 6600は全部で50台ほど販売されたほか、サブセットバージョンとしてCDC 6400やCDC 6500も開発される。が、これに並行してシーモア・クレイはより高性能なCDC 7600の開発に取りかかり、1969年に完成する。内部構造はよく似ているが、動作クロックは10MHz→36MHzに引き上げられるとともに、命令ユニットのパイプライン動作を可能にした。

メモリーもプライマリーが65Kwords、セカンダリーが最大512Kwords(1word=60bit)まで増量され、ピーク性能は36MFLOPSに達したとする。CDC 7600はおおむねCDC 6600の10倍の性能を目標にしたが、パイプライン化で約3倍、動作周波数の向上で約3.6倍となり、ほぼ目標は実現できたと言えよう。

ただ高性能化の一方で故障も多く(高密度化した内部回路の冷却機構が複雑で故障しやすかったらしい)、筐体も巨大で、最高速マシンの座は確保したものの、商業的に成功かというと、赤字にならない程度、というレベルであったらしい。

クレイはその後、CDC 7600を小型化するとともにこれを4台分まとめた形で性能を引き上げたCDC 8600の開発を始めるが、これはうまくいかず、同社が並行して開発を進めていたSTARプロジェクトと予算の奪い合いになる。

結果クレイはCDCを辞して自分の会社(Cray Research)を立ち上げることになるが、これは別に解説したい。次回はその後のCDCの動きについて説明しよう。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ