性能/消費電力比を非常に重視した設計の

Banias

Baniasのパイプラインは連載164回で解説したが、Pentium IIIまでのP6アーキテクチャーと大きな違いはない。実行ユニットそのものは対応する命令の増加などもあって強化されているが、その前段までの構造そのものはほぼ同じである。

Baniasでは絶対性能の改善そのものはあまり実現していない。また動作周波数も多少改善されてはいるが、0.13μmではTualatin-Sの1.4GHzがBaniasで最大1.7GHzになった程度なので、若干パイプラインのクリティカルパスを改善した程度のものである。

その代わりにBaniasでは性能/消費電力比を非常に重視した。これはモバイル向けであることを考えれば当然の話である。このために実装されたのがクロックゲーティング(Clock Gating)による省電力管理である。

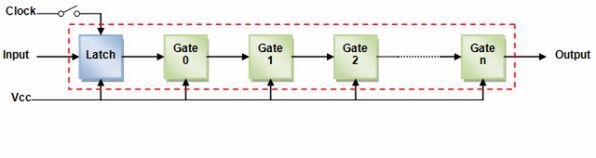

今でこそあたりまえになったクロックゲーティングであるが、この当時にコンシューマー向けのCPUで実装されていたのはBaniasだけだった。これは回路を細かくグループ分けしたうえで、必要のないグループにはクロック信号を供給しない仕組みである。

CMOSの消費電力はパッシブパワーとアクティブパワーの両方がある。パッシブパワーはいわゆるリーク電流に起因するもので、これはクロックゲーティングではどうにもならない(これをどうにかしたのがパワーゲーティングである)。

一方のアクティブパワーはクロック信号の周波数に比例する形で増えるが、従来は使われていない部分※にも無条件でクロック信号が供給され、これが消費電力を押し上げていた。

※:例えば、整数演算中は浮動小数点ユニットは遊んでいる。

クロック信号が供給されなければ、この部分での消費電力が減ることになる。もっとも「消費電力が減る」と簡単に言っても、実装は難しい。そもそもCPUはダイナミック回路といって、CPUのクロック信号がある程度以上あることを前提に構成されている。SpeedStepでもPowerNow!でも、最低動作周波数が決まっているのはこのためである。

ところが、クロック信号を完全に切ってしまうと、もう一度使いたいときにはクロック信号を供給してから、そのブロックを初期化する必要がある。この初期化には幾分かの時間を要するため、「ある命令を実行する際に次のブロックが現在止まっていたら再起動する」という手順ではレイテンシーが多くなりすぎる。

そこで、「まもなくこのブロックが利用される」というめどが立ったら実際に使われるより少し前にクロック信号の供給を開始して初期化しておかなければならない。

以上のことから、実際には単にクロック信号のスイッチ1個入れるだけでは足りず、再起動に必要な初期化回路や、どのタイミングでクロック信号の供給を再開するかの予測回路などもブロックごとに必要になる。

そうなると、ブロックを細かく分割するほどきめ細かな省電力化が実施できる反面回路規模が増えるわけで、どんな単位で分割するのが一番効果的かに関してはシミュレーションなどを繰り返して決める必要がある。当然回路そのものも、P6をそのまま流用するわけにはいかず、ほぼ再設計に近い作業となる。

→次のページヘ続く (市場を席巻したPentium M そして時代はCore Duoへ……)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ