市場拡大で長く続くであろう

28nmプロセスノード

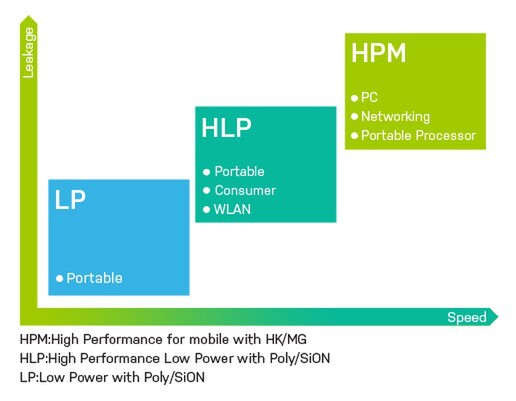

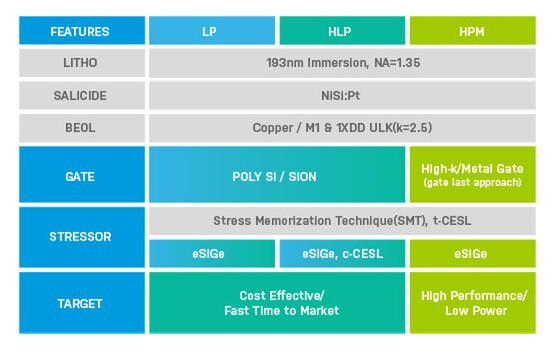

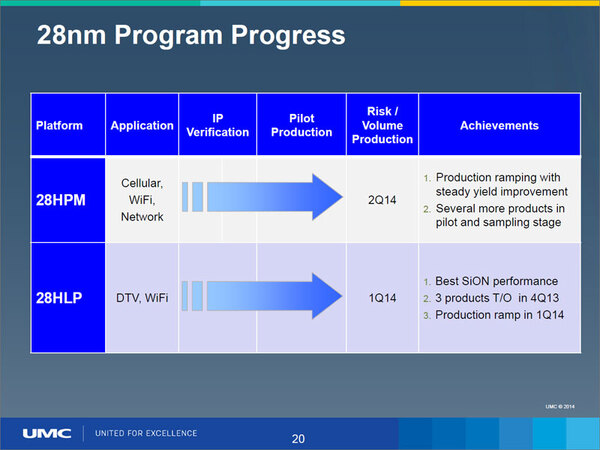

GLOBALFOUNDRIESに続いて、すでにリスク生産が開始されているのがUMCである。同社の場合、LP/HPL/HPMの3製品がラインナップされているが、このうちHPLは2014年第1四半期に、HPMは第2四半期にそれぞれリスク生産を開始している。

おそらく年末までには、同社の28nmプロセスで製造されたチップを搭載した最終製品が市場投入されるのはほぼ確実といったところで、立ち上がりこそは遅いがまぁまぁ順調といったところだ。

現時点で見えている範囲で、この28nm市場に最後に参入するのが中国SMICである。7月3日にQualcommの28nmベースのSnapdragonを量産する発表をしたことで業界を沸かせた。

同社は2014年1月に28nmプロセスの量産準備とロードマップを公表しており、“ものすごく”順調に行けば、今年中に量産チップを搭載した最終製品が市場に出てくる可能性がある。ただ現時点ではまだリスク生産も始まっていない状態なので、2015年に量産開始といった感じになりそうである。

ということで、28nmに関してはかなり順調になってきたのが昨今の状況である。これをやや別の角度から見てみたい。

TSMCによる最初の28nmプロセスのコストはおおむね、ウェハー1枚あたり7000~8000ドルといった価格であった。当時はなにしろ他に選択肢もないため、各社泣きながらもこの高いプロセス費用を支払っていた。

ちなみにこの時点で相対的に一番低コストだったのが40nmである。液侵を使えば大半の作業はシングルパターニングで露光ができたし、HKMGなどを使っていないからプロセスコストも比較的低めであった。そして同じ回路規模ならダイサイズが小さくまとまり、消費電力も減るため結局お得という、旧来のプロセス微細化の恩恵をストレートに受けた。

この動向が変わってきたのは2013年後半からである。まずTSMCの場合、初期のラインに関しては2年間の減価償却を済ませ、機器コストを価格に上乗せする必要がなくなったことで、相対的にウェハーの製造コストを下げられた。また、歩留まりの改善も低コスト化に貢献している。結果、ラインによってはウェハー1枚あたり6000ドル程度まで価格を下げられた。

この市場に殴りこみをかけたのがUMCとSMICである。UMCは、値下げしたTSMCのウェハーよりもさらに魅力的な価格を顧客に提示、SMICにいたってはそれをさらに大幅に下回る価格破壊と言ってもいいような価格を、まだ量産の見極めができる前から提示したとする。

すると業界がどの方向に進むかというと「28nmの低価格化」である。例えばTSMCは、すでに28nm HPCというプロセスを用意しつつある。このHPCというプロセスはTSMCの公式ページにはまだ出てこないが、HPMの低価格版という位置づけである。これに対応したIPもすでに用意されており、SidesenseというIPベンダーは5月末に、この28nm HPCに対応した組み込み向けメモリーのIPを発表している。

TSMCの28nm HPCはUMCなどと同等の、ウェハーあたり5000ドル近い金額まで下がるのではないかと見られている。これと同等の構成となるサムスンやGLOBALFOUNDRIESの28nmプロセスも、長期的には5000ドル近い価格まで落ちてくるだろう。

その一方、例えばUMCやSMICはHKMGを使わない低価格のプロセスをラインナップしており、こちらは条件次第ではウェハーあたり4000ドルを切る価格で生産できる模様だ。

こうなってくると、今の40nmに近い条件で28nmの生産が可能になってくる。もちろんこれは生産コストだけの話で、初期コスト、つまりテープアウトまでに必要な開発コストとマスクコストは相変わらず高騰しているが、昔に比べると多少ではあるが設計期間や検証などが容易になってきた※。

※:例えばARMは主要な製品についてはPOPもしくはHard IPを28nm向けに提供しているし、EDAツールも28nmへの対応が進んでいる。

28nmの低価格化により、少なくとも2020年頃までは28nmプロセスが広く使われるだろう、というのが業界の共通認識になってきている。

最先端のスマートフォン向けSoCや高性能CPUなどはもっと微細化が進んだプロセスが必要としても、100ドル程度のスマートフォンには28nmプロセスで製造できるSoCで十分、というのが現在の判断であり、こうしたものがより微細化したプロセスに以降するのは2017年以降とみられる。

2017年以降は、現在40~65nmプロセスで製造されている組み込み向けの様々なSoC類がほとんど28nmに以降を完了し、量産していると思われる。

もっとローエンドにあたるMCUは、現在は130~90nmが主体で、一部65nm~55nmを使ったハイエンド製品が混在する程度だが、現在28nmプロセスでの組み込み向けフラッシュメモリーの開発が進んでおり、やはり2017年頃には28nmでの生産が始まると見られている。

この市場は、特にIoT向けに低価格(1ドル未満)なセンサーノードが求められており、まずはダイサイズを極限まで減らし、可能ならセンサーを含む全コンポーネントをワンチップ化したいという要望が強く、このためには複雑な回路でもダイサイズを小さく抑えられる28nmプロセスが有利という判断だ。

モバイル向けSoCだけを見ているともうすこし28nmの世代は短いが、実際にはその後にまだまだ市場が広がると予測しており、ファンダリー各社はここでの低コスト化に向けた開発に余念がない。したがって、28nmノードはかなり長く続きそうである。

次のページヘ続く (中継ぎで終わる20nmと、その先の14nm)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ