CNTよりも技術的障害が低い

シリコンナノワイヤー

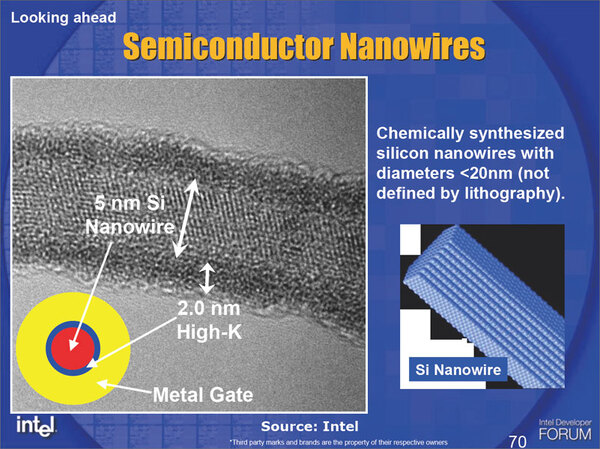

CNTと構造は似ているが、ベースとなるのがSiというのがSi Nanowireである。2005~2006年頃のインテルは、これに関してずいぶん盛んに研究成果をアピールしていた。

Si Nanowireはご覧の通り、極めて細いSiの配線である。これを利用することで、以下のメリットが生じる。

- 配線層が非常に微細なので、ゲートによる制御が容易になる。これにより短チャネル効果(つまりChannel Leakage)が大幅に抑制できる。

- 電子が散乱を受けずにSi格子内を移動する(バリスティック伝導)ため、トランジスタのスイッチング速度が大幅に向上する。

- Nanowireの直径をさらに細くした場合、表面の粗さがそのまま直径に大きく影響するようになる。この結果、量子力学的な効果でNanowireに島(クーロン島あるいは単電子島)と呼ばれる領域が生成される。これによりCBT(クーロン・ブロックゲート:Coulomb blockade thermometer)と呼ばれる現象が生じることになり、これを利用して単電子トランジスタ(SET:Single Electron Transistor)を生成可能になる。

単電子トランジスタというのは、要するに電子が1個流れるだけでスイッチングが可能になるトランジスタであり、On/Offの動作に必要となる電流を理論上最小まで抑えられる(これ以下には出来ない)というもので、究極の省電力トランジスタが生まれることになる。

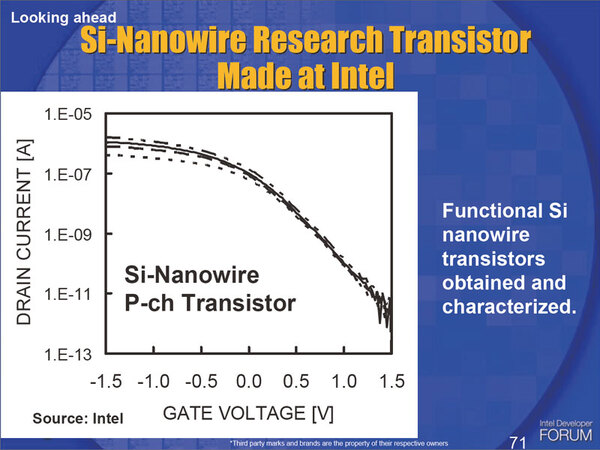

インテルの発表はまだここまで踏み込んだわけではないが、ゲート/ドレイン間にSi Nanowireを利用することで、良い特性を持つトランジスタが製造できたとアピールしている。

実はSi Nanowireそのものはむしろ、太陽電池の分野で研究が進んでいる。太陽電池の場合、発電量はSiの面積に比例するため、表面にSi Nanowireの突起を設けることで面積を増やせる。

入射光を閉じ込めて反射を抑えるような構造を作りやすいのもメリットとされるほか、そもそも従来のSi系太陽電池と比較した場合、PN接合の面積を大幅に増やすことも可能になっており、こうしたさまざまなメリットにより発電量をずっと大きくできるものと期待されている。

そんなわけで、ロードマップによってはCNTよりもずっと前にこのSi Nanowireが実現化されるとしているケースもあるが、実情は「CNTよりも技術的障害は低いんじゃないか」程度の話であって、やはり実現時期がさっぱり見えていないのである。

例えばこのページの最初の画像も、実際には化学合成によって製造するものなので、既存のCMOSなどの製造プロセスとまったくく互換性がない。

ただ、最近はもうすこし進歩している。下の画像はSOIウェハーの製造を手がけるSOITECが、55nmプロセスを利用してSOI基板上にSNFET(Silicon Nanowaire FET)を製造した例である。

こうした「もうすこし」現実的な製造方法が模索されつつある。とはいえ、こちらもまだCMOSを構成するための方法は確立されていないし、上の画像もあくまで実験室レベルの話だから量産手法をこれから考えないといけないなど、まだまだ前途多難と見られている。

ビームをウェハーに当て、回路を描画する

電子ビーム露光

ここからはトランジスタ構造とは関係ない、プロセス周辺の話である。1つ目は露光のプロセスだ。連載252回でEUVを解説した。これは波長が13.5nmのEUV(極端紫外線)を使うことで、露光を一回で済ませられる、つまりマルチパターニングの必要がないというものだ。

EBL(Electron Beam Lithography:電子ビーム露光)は、EUVや今のArF(フッ化アルゴン)ベースの露光と異なり「細く絞った電子ビームをウェハーに当てることで、直接回路パターンを描画する」仕組みである。つまり、EBLを使うとマスクがいらなくなる。

すでにEBLをベースとした露光装置は存在しており、現在マスクの製造を含む幅広い用途に利用されている。例えばアドバンテストのF7000というEB露光装置は、2013年中に3台出荷されていることが発表されている(関連記事)。

その意味では冒頭に書いた「未来の技術扱いされるほどに展望が見えていない」とは違うのではないか、という声も出てきそうだが、やはり展望が見えていない。その最大の理由は、低いスループットである。

現状、EUVは50~80W程度の出力しかなく、これでは処理能力は50wph(50枚/時)に満たないレベルであるが、EBLだと「1日数枚」のレベルである。もちろんマスクのようにに、「1枚作ればいい」ものであれば、これは許容範囲であるが、半導体量産の現場でこの処理能力は論外である。

これに関しても、例えば繰り返しパターンが続く箇所(SRAMを使ったキャッシュなどその典型例である)を、アパチャー(電子ビームを絞り込む部分)に作りこむという部分一括露光方式などを組みあわせて処理能力を引き上げる策を色々講じているが、それでも1wphを実現するのは難しいと見られている。

こちらもEUVと根は同じで、とにかく出力を上げるのが難しい。困難さではEUVよりもさらに難しいと見られており、「超少量多品種」あるいは「マスクの製造」などはともかく、半導体量産の現場に導入するというロードマップは現在のところ皆無である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ