NTVを利用したインテルのプロセッサー

Claremont

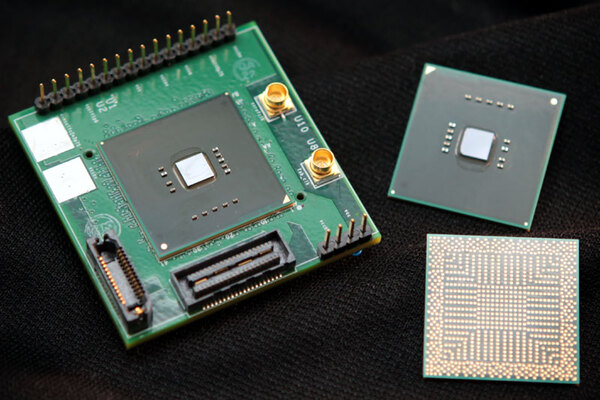

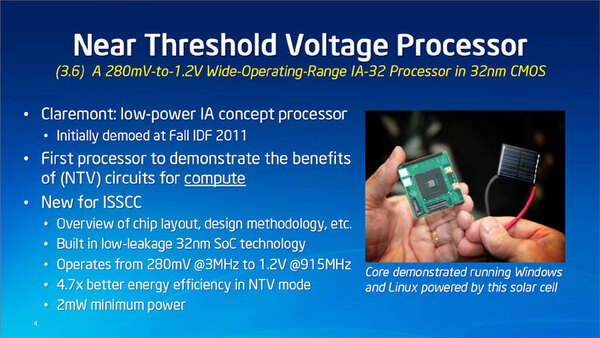

前提の知識を詰め込んだところで、いよいよ本題に入ろう。インテルはここ数年、NTV/STV領域に関してずいぶん研究を積み重ねている。2011年におけるIDFの折に、突如示されたのがClaremontである。

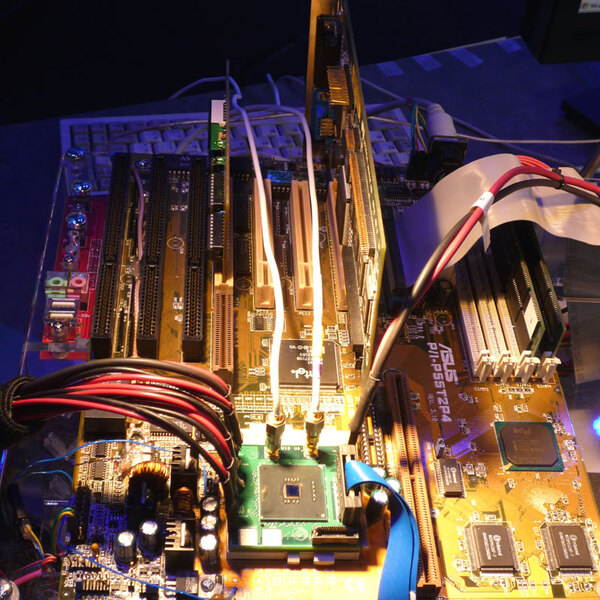

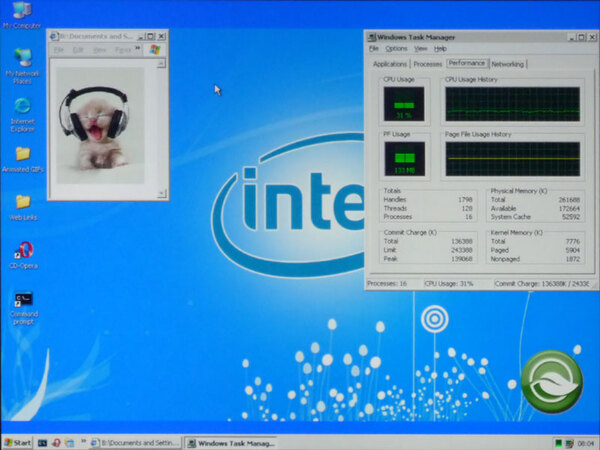

基調講演では、このCleamontが搭載されたマザーにWindowsをインストールし、Cleamontそのものは太陽電池で動作する(太陽電池への明かりを遮った瞬間に、タスクマネージャーや左上の謎アプリが停止する)ことをデモした。

このCleamontはIntel Labsが低消費電力の実証のために開発したもので、まさしくNTVを利用したものである。翌2012年のISSCCにおいてインテルは、Cleamontの詳細を説明しているので、もう少し細かく説明したい。

CreamontのコアはPentium

低電圧動作のために回路を変更

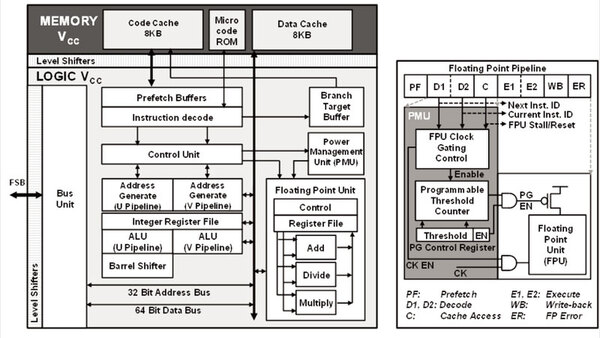

下の画像がCreamontの内部構造である。言うまでもなくPentiumそのもので、このレベルでの違いはバスユニットとFSBの間に挟むレベルシフターのみである。レベルシフターというのは電圧変換である。

Socket 5世代の信号電圧は3.3Vになるが、Cleamontの内部は上の画像にもあるように0.28V~1.2Vという非常に低い電圧なので、このまま信号を出力してもSocket 5に適合しない。そこで電圧変換を掛けて3.3Vにするのがこのレベルシフターの仕事である。

ただしこれはあくまで論理回路レベルの話だ。物理実装に関しては、超低電圧動作に備えて内部の構造を最適化したり、セルライブラリーに手を入れたりしたことが論文で説明されている。ただプロセスそのものはあくまで既存の32nmプロセスで、ここで低電圧動作を可能にするように回路を工夫したという話である。

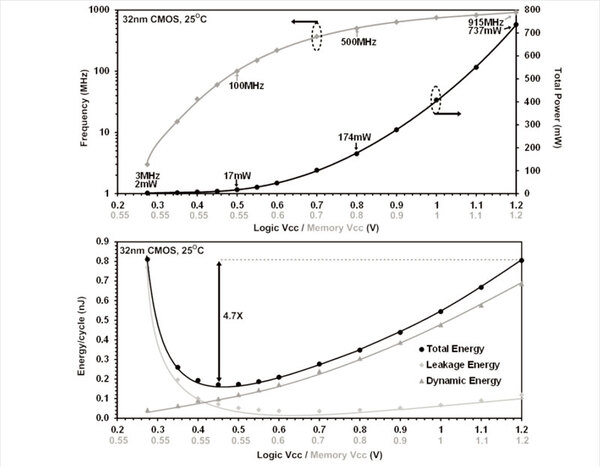

さて、結果の一番重要な部分は上のグラフである。まず上のグラフの薄い線が動作周波数(縦軸左)、濃い線が消費電力(縦軸右)である。一番低い0.28V付近では3MHz動作で、消費電力はわずか2mWである。ここから電圧をあげてゆくと、0.5Vの時に100MHz/17mW、0.8Vの時に500MHz/174mWになり、1.2Vまで引き上げると915MHz/737mWという結果になる。

これを1サイクルあたりの消費電力、という観点で描き直したのが下側のグラフになる。こちらではDynamic EnergyとLeakage Energy、つまりアクティブな消費電力とリーク電流に起因する消費電力をそれぞれ測定した上で、これを1サイクルあたりの消費電力として示している。

まずリークに関しては、電圧を下げることでリーク電流そのものは減るのだが、それよりも動作周波数が下がる勢いの方が強いので、1サイクル分の時間に占めるリーク電流の割合は急激に増えることになる。

逆に電圧を上げると動作周波数が上がるので、1サイクル分の時間に占めるリーク電流の割合は0.7V付近までどんどん減っていくが、その先になると電圧上昇によるリーク電流増加の割合が、動作周波数の上がる割合を超えて増えるので、結果としてまた次第に増えていくことになる。一方アクティブな消費電力が、ほぼ電圧の2乗に比例して増える。

この結果、1サイクル分の消費電力という観点では、0.45V付近(動作周波数は60MHz付近)が一番効率が良く、0.2 nJ/サイクル弱に抑えられる。逆に0.28Vや1.2Vといった領域では0.8 nJ/サイクル強の消費電力となり、この差が4.7倍にも達するという結果である。

余談になるが、このCleamontをベースにしたのがインテルの低消費電力SoC「Quark X1000」である。コアそのものは400MHz動作ということで、上側のグラフを見ると動作周波数は100mW程度になるから、Quark X1000に関してもコアそのものは0.7V程度だと想像される。

実際にはTDPが2Wというのは、コア以外にSRAMやチップセット機能などを全部てんこ盛りにしているためであると考えれば良い(関連記事)。

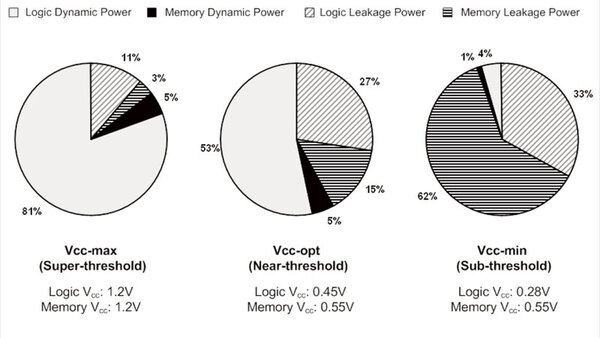

この消費電力の内訳を円グラフで示したのが下の画像だ。特にVcc-min(コア電圧が0.28V)の時を見ると、62%がメモリーのリーク電流に起因し、33%がロジック部のリーク電流に起因する。

逆に言えばメモリーを同じようにNTV動作させれば、さらにリークが減らせる“可能性がある”が、これが簡単にできないからこその結果であるとも言える。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ